低コスト・大面積な有機エレクトロニクスの鍵

2020-03-13 産業技術総合研究所

発表のポイント

- 電子素子を動作させるためには、電圧や電流を入出力する電極を半導体に取り付けますが、電極形成の際に半導体が受けるダメージや電極と半導体の接触不良などがないよう常に考慮する必要があります。

- 今回、高精細にパターニングされた電極を基板から引き剥がし、これを有機半導体の上に移し取る手法を開発しました。これにより、わずか1分子層の有機半導体であっても半導体本来の機能を引き出せることを実証しました。

- 安価で汎用性が高く、環境負荷の小さい材料を使用しており、大面積化が容易で、しかもさまざまな表面形状へ適用できることから、ソフトエレクトロニクスデバイスの社会実装だけでなく、バイオエレクトロニクス分野への貢献が期待されます。

発表概要

東京大学大学院新領域創成科学研究科、同マテリアルイノベーション研究センター、産業技術総合研究所 産総研・東大 先端オペランド計測技術オープンイノベーションラボラトリ(注1)、物質・材料研究機構 国際ナノアーキテクトニクス研究拠点(WPI-MANA)の共同研究グループは、洗濯のりにヒントを得て、高精細にパターニングされた電極を有機半導体に取り付ける手法を開発しました。

さまざまな機能性を有する電子素子を駆動させるためには、電圧や電流を入出力するための電極が必要不可欠です。電極は通常金属で、高真空下で大きなエネルギーを用いて成膜されることが多く、電極の設置面へのダメージを抑え、接着力など下地との相性を最適化することも重要な課題でした。

本研究グループは、洗濯のりの成分であるポリビニルアルコールが乾燥すると固まり、水にあうと簡単に溶けることを利用し、基板上で高精細にパターニングされた電極をポリビニルアルコールなどとともに電極フィルムとして引き剥がし、半導体上に移し取る手法を開発しました。さらに、たった1分子層(厚さ4ナノメートル)からなる有機半導体に金属電極を取り付け、半導体の機能を十分利用できることを実証しました。取り付け先の制約は極めて少なく、曲面や生体などへの応用も期待できます。今回の成果により、さまざまな積層デバイスへの応用が可能となり、将来の産業応用における低コスト・フレキシブルエレクトロニクス用のプロセスとしての利用が見込まれます。

本研究成果は、英国科学雑誌「Scientific Reports」2020年3月13日版に掲載されます。本研究は、日本学術振興会(JSPS)科学研究費補助金「単結晶有機半導体中電子伝導の巨大応力歪効果とフレキシブルメカノエレクトロニクス」「有機単結晶半導体を用いたスピントランジスタの実現」(研究者代表者:竹谷 純一)の一環として行われました。

発表内容

[背景]

半導体はさまざまな電子デバイスにおいて重要な役割を担っており、現在はシリコンをはじめとする無機半導体が広く用いられています。半導体をセンサや論理演算などの機能素子として利用するには、電圧や電流を入出力するための電極を半導体上に形成する必要があります。電極は通常金属で、真空蒸着法(注2)やスパッタリング法(注3)など多大なエネルギーを要するプロセスを用いて形成されることが多く、高エネルギーに伴う半導体へのダメージを抑える必要がありました。また、接着力不足などに起因する半導体との接触不良を解決することも重要な課題でした。このような金属電極を形成する際の問題は、フレキシブルエレクトロニクスの基盤材料である有機半導体の分野において顕在化しています。

有機半導体は、塗って乾かすだけで高品質な結晶性薄膜が低コストで得られるため、RFIDタグ(注4)や種々のセンサといった膨大な数のデバイスが必要となるIoT時代の基盤材料として近年盛んに研究されています。しかしながら、原子同士が共有結合で強く結びついている無機半導体と比較して、分子同士が弱い分子間力によって集合している有機半導体は、溶剤や熱によるダメージを受けやすいという課題がありました。例えば、有機電界効果トランジスタ(OFET: 注5)では、有機半導体や電極といった構成要素を積層して作製しますが、有機半導体上への電極形成時に、熱によるダメージやパターニングに必要な溶剤によるダメージを抑える必要がありました。

[手法と成果]

このような課題を解決するため、電極をあらかじめ別の基板上に作製し、半導体上に移し取るというアプローチに取り組んできました。基板上に作製した電極を直接半導体表面に移し取るには、基板から電極を引き剥がすため、電極を半導体に十分な強度で接合する必要があります。しかし、半導体と電極は直接触れて電気的につながっている必要があるため、間に接着層を挟むことができず、強く接合するのは困難です。そこで、さまざまな基板や作製プロセスを検討してきました。そのうち、洗濯のりが乾燥すると固まり、水にあうと簡単に溶けることにヒントを得て、「のり」を使って基板から電極を引き剥がし、後で「のり」を除去するという発想に至りました。さらに、電極を薄い保護層で覆えば、半導体と保護層との静電気力を利用して電極を半導体に接触させられるのではないかと考えました。

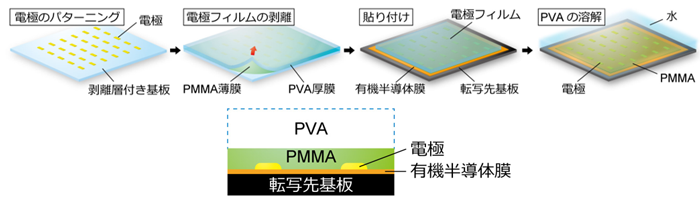

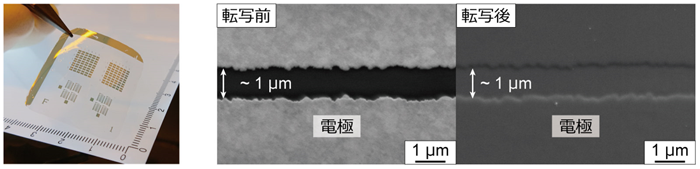

こうしてたどり着いた半導体上への電極の取り付け手法を図1に示します。本手法では、基板上でパターン化された電極を半導体上に移し取るため、安価で広く用いられている2種類の高分子を使用しました。1つ目は、アクリル樹脂の一種であるポリメタクリル酸メチル(PMMA)、2つ目は洗濯のりの成分として知られ、水によく溶けるポリビニルアルコール(PVA)です。まず、基板上で電極材料をパターニングし、その上に薄いPMMAを塗布します。これらはいずれも厚さ数10~100ナノメートル(1ナノメートルは10億分の1メートル)と薄いため、このまま取り扱うことが困難です。そこで、その上にPVAを20~30マイクロメートル(1マイクロメートルは100万分の1メートル)の厚さに塗って乾かします。その後、電極、PMMAおよびPVAを一括して基板から引き剥がすことで、取り扱いが容易な電極フィルムを得ました(図2左)。続いて、電極フィルムを半導体上に貼り付け、温水でPVAを溶解して除去すると、薄い電極およびPMMAが静電気力によって半導体上に吸着します。以上の簡便な手法により、1マイクロメートルという高精細でパターニングされた電極を、プロセス中に伸縮することなく半導体上に移し取ることに成功しました(図2右)。

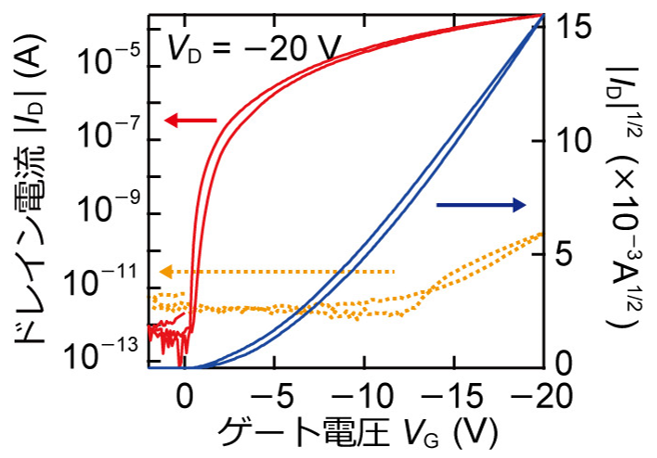

開発した手法の有用性を確かめるため、1分子層(厚さ4ナノメートル)の単結晶からなる有機半導体の上に電極を取り付けてOFETを試作しました。従来の真空蒸着法で電極形成したOFETでは、ゲート電圧を変化させてもドレイン電流が殆ど流れないことから、熱的なダメージによって特性が大きく低下しています(図3橙色の破線)。一方、開発した手法で作製したOFETは、ゲート電圧を変化させると有機半導体の本来の性能であるドレイン電流値を示し(図3赤色の実線)、ゲート電圧とドレイン電流の平方根(図3青色の実線)の関係から移動度(注6)を求めたところ、実用化の指標となる10 cm2/Vs程度を示し、1分子層の有機半導体が持つ性能を引き出せることが実証できました。

図1 上)有機半導体膜上への電極の転写手法模式図。

下)デバイスの断面図。

図2 左)作製した電極フィルムの写真。

右)半導体膜上への転写前後の電極の走査型電子顕微鏡(SEM)像。

図3 作製した単分子層のOFETの飽和領域の伝達特性(実線)および従来の真空蒸着法によって電極を作製したOFETの伝達特性(橙色破線)。図中のVDはドレイン電圧。

[今後の展望]

この手法を用いることで、積層デバイスの作製が容易となるため、より複雑で高度な機能を実現する集積回路の作製が可能となります。

また、安価で汎用性が高く環境負荷の小さいPMMAやPVAを使用していることや、大面積化が容易で、曲面などさまざまな表面形状の半導体にも適用できるなど、電極を取り付ける半導体側の制約が少ないことも特長です。今後、こうした特長が活かせる有機半導体を用いたソフトエレクトロニクスの社会実装やバイオエレクトロニクス分野への貢献が期待されます。

発表者

牧田 龍幸(東京大学大学院新領域創成科学研究科物質系専攻 博士課程2年生)

渡邉 峻一郎(東京大学大学院新領域創成科学研究科物質系専攻 特任准教授/産業技術総合研究所 産総研・東大 先端オペランド計測技術オープンイノベーションラボラトリ 客員研究員 兼務)

竹谷 純一(東京大学大学院新領域創成科学研究科物質系専攻 教授/マテリアルイノベーション研究センター(MIRC) 特任教授 兼務/産業技術総合研究所 産総研・東大 先端オペランド計測技術オープンイノベーションラボラトリ 客員研究員 兼務/物質・材料研究機構 国際ナノアーキテクトニクス研究拠点(WPI-MANA)MANA主任研究者(クロスアポイントメント))

発表雑誌

雑誌名:「Scientific Reports」(オンライン版:3月13日)

論文タイトル:Damage-free Metal Electrode Transfer to Monolayer Organic Single Crystalline Thin Films

著者:Tatsuyuki Makita, Akifumi Yamamura, Junto Tsurumi, Shohei Kumagai, Tadanori Kurosawa, Toshihiro Okamoto, Mari Sasaki, Shun Watanabe*, and Jun Takeya*

DOI番号:10.1038/s41598-020-61536-8

用語の説明

- (注1)産総研・東大先端オペランド計測技術オープンイノベーションラボラトリ

- 平成28年6月1日、東大柏キャンパス内に設置した産総研と東大の研究拠点。相互のシーズ技術を合わせ、産学官ネットワークの構築による「橋渡し」につながる目的基礎研究の強化や、先端オペランド計測技術を活用した生体機能性材料、新素材、革新デバイスなどの産業化・実用化のための研究開発を行っている。

- (注2)真空蒸着法

- 真空中で金属などの材料を加熱することで蒸発あるいは昇華させ、基板表面に堆積させる手法。

- (注3)スパッタリング法

- 真空中で金属などターゲットにイオン化させた希ガス元素を衝突させることで、はじき飛ばされた原子を基板表面に堆積させる手法。

- (注4)RFIDタグ

- 電波を用いた無線通信により、個別識別コード情報(ID)をやり取りするタグ。Suicaなどの交通カードもRFIDタグに含まれる。

- (注5)有機電界効果トランジスタ(OFET)

- 有機半導体を活性層とした電界効果トランジスタ。電界効果トランジスタは、スイッチング素子や増幅素子として利用され、集積回路において必要不可欠な電子素子である。一般的なトランジスタ同様に、ソース・ドレイン電極間にドレイン電圧(VD)を印加することで流れるドレイン電流(ID)をゲート電極に印加されるゲート電圧(VG)によって制御できる。

- (注6)移動度

- 電場により電荷が移動する際の移動しやすさを表す量。IoTデバイスの動作には10 cm2/Vs以上の移動度が望ましい。