サービス最適化を高速化して、事業者のビジネスチャンス拡大に貢献

2018-05-29 産業技術総合研究所 東京大学情報基盤センター

ポイント

- 「人工知能」技術の一つである機械学習の訓練処理を高速化する計算方式と回路を考案

- 高速化が難しい訓練処理の処理能力を最大で5倍に向上できることをシミュレーションで確認

- 時間がかかる訓練処理の高速化によりサービス事業者のビジネスチャンス拡大への貢献に期待

概要

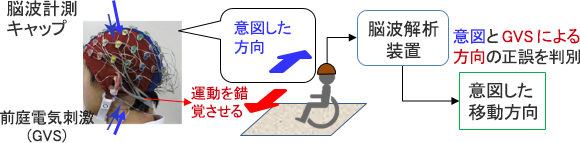

国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 中野 隆志】ナノCMOS集積グループ 大内 真一 主任研究員と情報技術研究部門【研究部門長 田中 良夫】サイバーフィジカルクラウド研究グループ 高野 了成 研究グループ長は、東京大学情報基盤センター工藤研究室と共同で、機械学習での訓練処理の時間を短縮する計算方式と回路を考案した。機械学習は、入力をモデルにより処理し識別結果や将来の予測などを出力する推論処理と、大量のデータを学習し、よりよいモデルを構築する訓練処理からなる。推論処理の高速化手法は多いが、訓練処理の高速化手法は決定的なものがなく、長時間の処理が必要であった。通常、訓練処理は、32ビットか16ビットの数値計算で行われるが、今回提案した計算方式では、9ビットの数値計算により、訓練処理に要する時間を大幅に短縮できると同時に、必要な乗算、加算の精度を確保できる。また、この計算方式を実現できる回路を考案し、シミュレーションにより、単位消費電力あたりの処理能力が従来方式の約5倍まで向上することを確認した。この技術は、再構成可能なハードウエアであるFPGAを用いた機械学習システムや、機械学習専用プロセッサで用いられることが期待される。

なお、この技術の詳細はイタリア・フィレンツェで開催される「IEEE国際回路・システム会議」(2018 IEEE International Symposium on Circuit and System)にて、5月28日(中央ヨーロッパ時間)に発表される。

機械学習での処理の流れと今回提案した計算方式の適用例

開発の社会的背景

機械学習は、交通、サービス、コンサルティング、医療、製造など、さまざまな分野でビッグデータに基づくサービス提供に広く利用されている。機械学習では、訓練処理により生成するモデルの善し悪しが推論の正確性を左右するため、大量のデータを用いた訓練処理が必要である。さらに、訓練処理には推論処理と比べて高い数値計算精度が要求されるため、非常に大きな処理能力が必要である。このため処理に要する時間や消費電力が問題になっている。

研究の経緯

産総研ナノエレクトロニクス研究部門と情報技術研究部門は、2016年度より新エネルギー・産業技術総合開発機構(NEDO)のプロジェクト「IoT推進のための横断技術開発プロジェクト(2018年度より『高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発』)」で、東京大学情報基盤センター工藤研究室などと共に、「省電力AIエンジンと異種エンジン統合クラウドによる人工知能プラットフォーム」に関する共同研究を行っている。今回の研究は、その一環として行われた。

研究の内容

機械学習の訓練処理では通常32ビットか16ビットの数値表現が用いられる。一般に、数値を表すビット数を大きくすると計算精度が向上する一方で、処理を行う回路の規模が大きくなり、処理時間や消費電力が増大する。逆に、ビット数を小さくすると、回路規模が小さくなり処理時間や消費電力は減少するが、計算精度が悪くなる。今回、機械学習の訓練処理で現れる数値の範囲を解析して、限られたビット数で全てのデータを精度よく表現できるデータ形式と、ビット数が小さくても、訓練処理で用いられる乗算、加算が正確に行える計算方式を考案した。

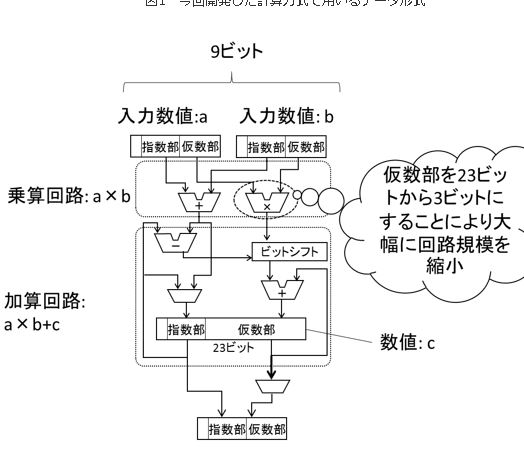

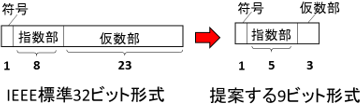

図1に、IEEE標準の32ビットデータ形式と、今回考案した9ビットデータ形式を示す。32ビットデータ形式は符号1ビット、指数部8ビット、仮数部23ビットで構成されるのに対し、今回の9ビットデータ形式は、符号1ビット、指数部5ビット、仮数部3ビットで構成される。32ビット形式の場合、演算回路の約80%を乗算回路が占める。9ビットデータ形式では仮数部が23ビットから3ビットに減ったため、乗算回路が32ビット形式と比べて1/30程度となる。更に、指数部のビット数を8ビットから5ビットとし、演算回路への入力を32ビットから9ビットに減らしたことにより、データをメモリーなどから演算回路まで移動させるのに必要なエネルギーも約1/4まで削減できる。

一方、生成したモデルを用いた推論の精度に大きく影響する加算回路は、仮数部を23ビットとして学習精度を保つ。これは、数値計算の精度劣化を引き起こす「情報落ち」を防ぐためであり、これによって、機械学習の訓練処理も精度が向上する。加算回路では仮数部を23ビットと増やしても回路全体の大きさへの影響は少ない。

図1 今回開発した計算方式で用いるデータ形式

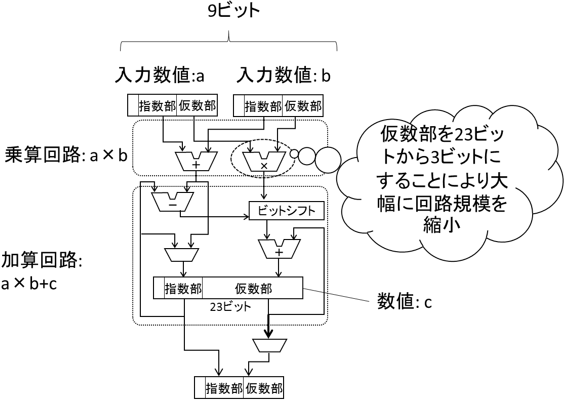

図2 今回開発した計算方式を実現する演算回路

図2に、今回考案した計算方式を実行する回路を示す。機械学習の訓練処理では、2つの数値a、bを乗算し、内部に保存された数値cに加算する「積和演算」を多用する。今回の回路では、まず2つの入力を9ビット形式で受けつけ乗算する。次に、乗算結果の仮数部を23ビットに変換し、ビットシフト処理によって桁あわせした後、23ビットで加算を行う。加算結果は再び9ビット形式に変換されて出力される。この計算方式と回路について、シミュレーションによって推論の精度や、消費電力を推定した。32ビット形式を用いた場合と比べて、9ビット形式を用いて生成したモデルによる推論の精度の劣化は2%程度に抑えられた。一方、9ビット形式を用いることにより、回路規模を1/5程度に縮小できると推定され、必要な消費電力は1/5程度に低減できると推定された。回路規模と消費電力が1/5程度となるということは、同一規模のハードウエアを用いた場合には5倍程度の高速化を実現できることになる。

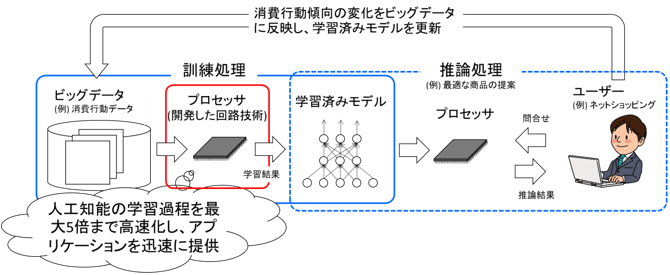

今回考案した回路が実装されたプロセッサを用いれば、機械学習を用いたサービスを最適化する場合などに訓練処理を大幅に短縮できると期待される(概略図参照)。たとえば、ネットショッピングの履歴を参考に最良の商品を提案するような推論処理をする場合を考える。消費行動の傾向が変わり、モデルをこれに追従して最適化したい場合には、ビッグデータに基づいて訓練処理を行ってモデルを改良する。この訓練処理によるモデルの改良にかかる時間が大幅に短縮されれば、サービス事業者は新たなビジネスチャンスを獲得できると共に、利用者の利便性も向上する。

今後の予定

今回の成果では、数値を表すビット数を9ビットとすると高速化できるとわかったが、機械学習によって推論を行う問題によっては8ビット形式でも十分な精度で学習できることも分かっている。今後は更に多くの問題で今回提案した方式の有効性を検証すると共に、ハードウエアを試作して実現可能性を検証し、実用化を進める。

用語の説明

- ◆ビット

- 計算機の中で扱われるデータ、数値の最小単位である2進数一桁をさす。

- ◆シミュレーション

- ここでは、機械学習用のソフトウエアを、今回提案した計算回路を模したコンピュータプログラムによって検証する模擬試験をさす。今回は、プリファードネットワークス社が開発した機械学習プログラムChainerに2進数処理を行う拡張機能を追加して、計算回路の処理を模擬した。

- ◆FPGA

- Field Programmable Gate Arrayの略で、デジタル信号処理を行う回路要素をユーザーが任意に組み合わせて計算回路を構成できる半導体チップ。

- ◆IEEE標準

- ここではIEEE (The Institute of Electrical and Electronics Engineers, Inc.)が標準として定めた、IEEE754, IEEE Standard for Floating-Point Arithmetic(浮動小数点算術に関する標準)を指す。符号ビット、指数部ビット、仮数部ビットから成り、合計ビット数が16ビット、32ビット、64ビットとなるものをそれぞれ、半精度、単精度、倍精度と称する。

- ◆指数部、仮数部

- ここでは、IEEE標準で定められた2進数浮動小数点表示の部分に関する呼称を指す。IEEE標準では任意の数値を、2進数の小数(仮数部)と位取りを表す指数部とに分けて表現する。

- ◆情報落ち

- 2つの数を加減算する際に、2数の絶対値が大きく異なると、絶対値の小さな数が加減算できなくなる現象。