直径5ナノメートル以下の磁気トンネル接合素子で高速動作を実証

2021-12-14 東北大学,科学技術振興機構

ポイント

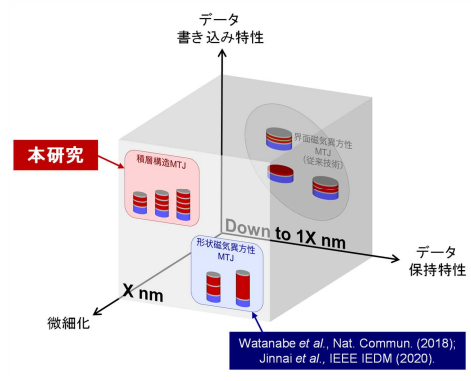

- 磁気抵抗メモリーで記憶を担う磁気トンネル接合素子の高速動作を特徴づけ、時定数を制御できる新構造を提案

- 直径5ナノメートル以下の素子で10ナノ秒以下の高速書き込み動作を実証

- オングストローム世代半導体製造技術での磁気抵抗メモリー基盤技術を確立

DXおよびカーボンニュートラル(脱炭素)社会の実現に必要不可欠な半導体の分野ではし烈な技術競争が行われています。中でも、スピントロニクス技術を利用した不揮発性メモリーであるスピン移行トルク磁気抵抗メモリー(STT-MRAM)並びにそれを混載メモリーに適応した省電力ロジックは、半導体集積回路の大幅な低消費電力化をもたらすと期待され、特に注目されています。しかし、将来の微細世代技術に適用して社会実装を促進するためには、記憶素子の微細化と加えて高速動作に関する性能の向上が求められていました。

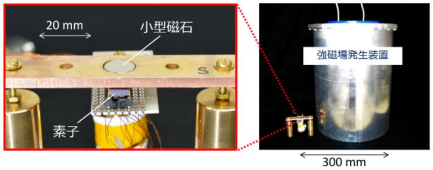

東北大学 材料科学高等研究所の陣内 佛霖 助教、電気通信研究所の五十嵐 純太 学術研究員、深見 俊輔 教授、大野 英男 教授(現 総長)らは、高速書き込み動作を特徴づける時定数を制御できる磁気トンネル接合(MTJ)(STT-MRAMの情報記憶素子)の構造を提案し、5ナノメートル以下の直径を持つMTJ素子で3.5ナノ秒までの高速書き込み動作を実証しました。これは、STT-MRAMが将来のオングストローム世代半導体製造技術でのSRAMや高速DRAMの代替として使えることを示す重要な成果です。本研究により、超大容量・低消費電力・高性能不揮発性メモリー、およびそれを用いた超高性能・低消費電力半導体集積回路の開発が加速することが期待されます。

本研究成果は、2021年12月11-15日(米国時間)に米国サンフランシスコで開催される、半導体素子に関する世界で最も影響力のある学術会議、「米国電子情報学会(IEEE)主催の国際電子デバイス会議(International Electron Devices Meeting)」で発表されます。

本研究は科学技術振興機構(JST) 産学共創プラットフォーム共同研究推進プログラム(OPERA)「世界の知を呼び込むIT・輸送システム融合型エレクトロニクス技術の創出:領域統括 東北大学 遠藤 哲郎」、日本学術振興会(JSPS) 科学研究費助成事業などの支援により行われました。

<論文タイトル>

- “Fast Switching Down to 3.5 ns in Sub-5-nm Magnetic Tunnel Junctions Achieved by Engineering Relaxation Time”

<お問い合わせ先>

<研究に関すること>

深見 俊輔(フカミ シュンスケ)

東北大学 電気通信研究所 教授

<OPERAプロジェクトに関すること>

遠藤 哲郎(エンドウ テツオ)

東北大学 国際集積エレクトロニクス研究開発センター センター長・教授

<JST事業に関すること>

伊藤 哲也(イトウ テツヤ)

科学技術振興機構 イノベーション拠点推進部OPERAグループ

<報道担当>

東北大学 材料科学高等研究所 広報戦略室

科学技術振興機構 広報課