2022-06-12 東京大学

○発表者:

小林 正治(東京大学 生産技術研究所 准教授)

浦岡 行治(奈良先端科学技術大学院大学 先端科学技術研究科 教授)

○発表のポイント:

◆酸化物半導体を三次元構造へ均一に成膜する技術を開発し、高密度かつ低消費電力である三次元垂直チャネル型の強誘電体および反強誘電体トランジスタメモリを実現した。

◆従来のスパッタ法ではなく原子層堆積法による成膜により、酸化物半導体の三次元集積メモリデバイスへの応用の可能性が開けた。また、強誘電体に加えて反強誘電体を用いることでメモリの書き換え動作を効率的に行うことができる。

◆このメモリデバイス技術をIoTデバイスのストレージメモリに用いることで、ビッグデータを利活用する社会サービスの展開が期待される。

○発表概要:

IoT家電などのIoTデバイスで取得するデータ量は年々増大し、クラウドサーバーでのデータトラフィックを逼迫していきます。ビッグデータを有効に利活用するためには、IoTデバイスでも大量のデータを蓄積し、AIアルゴリズムによる情報処理が求められてきます。大容量のストレージメモリとしてはNANDフラッシュメモリ(注1)が一般的ですが、消費電力が大きくIoTデバイスへの搭載には不向きです。強誘電体トランジスタ(FeFET)(注2)メモリは、強誘電体の性質から消費電力が小さいですが、NANDフラッシュメモリのように高密度な三次元垂直チャネル構造の実現可能性は明らかになっていませんでした。

そこで、東京大学 生産技術研究所の小林 正治 准教授と奈良先端科学技術大学院大学の浦岡 行治 教授らの共同研究グループは、酸化物半導体(注3)である酸化インジウム(In2O3)を従来のスパッタ法(注4)に代わる原子層堆積(ALD)法(注5)で成膜する技術を開発し、三次元垂直チャネル型の強誘電体および反強誘電体(注6)トランジスタメモリの開発に成功しました。

本メモリデバイス技術は高密度かつ低消費電力であるため、IoTデバイスのストレージメモリに用いることで、ビッグデータを利活用する社会サービスの展開が期待されます。

○発表内容:

<研究の背景と経緯>

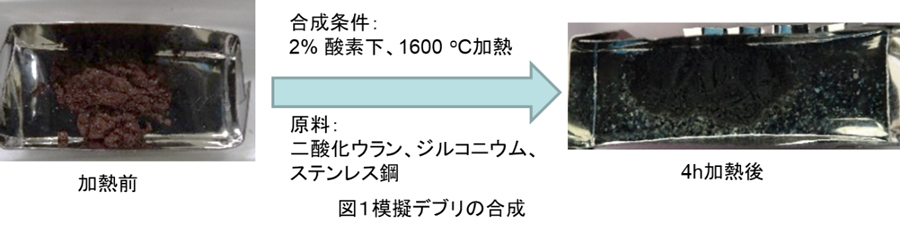

IoTデバイスで取得するデータ量は年々増大し、クラウドサーバーでのデータトラフィックを逼迫してきます。ビッグデータを有効に利活用するためには、IoTデバイスでも大量のデータを蓄積し、AIアルゴリズムによる情報処理が求められてきます。大容量のストレージメモリとしてはNANDフラッシュメモリが一般的ですが、消費電力が大きくIoTデバイスへの搭載には不向きです。強誘電体トランジスタ(FeFET)メモリは、強誘電体の性質から消費電力が小さいですが、NANDフラッシュメモリのように高密度な三次元垂直チャネル構造のFeFETの実現可能性は明らかになっていませんでした。特に、三次元NANDフラッシュメモリのようにチャネルにポリシリコンを用いると、ポリシリコンの低移動度による読出し速度の低下や、強誘電体とポリシリコンの間に低誘電率の界面層が形成され電荷捕獲による信頼性劣化や書き込み電圧が低くできなくなる、といった課題があります。この課題に対し東京大学 生産技術研究所の小林 正治 准教授らは、IGZOなどの酸化物半導体をチャネルとするFeFETメモリを提案(図1(a))し、理論的にその実現可能性と有用性を示してきました。しかし酸化物半導体を三次元構造へ均一に成膜するには従来のスパッタ法では成膜の直進性が高く難しいという技術的課題があり、ALD法が望まれていました(図1(b))。

<研究の内容>

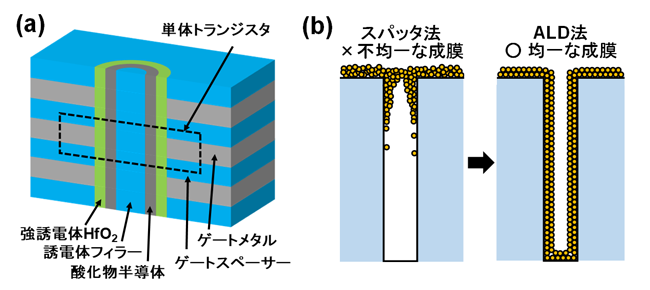

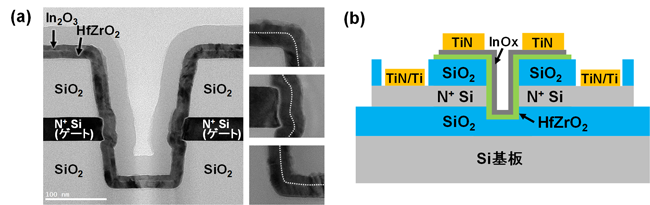

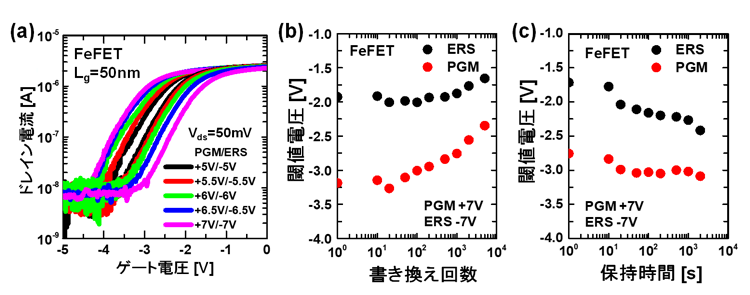

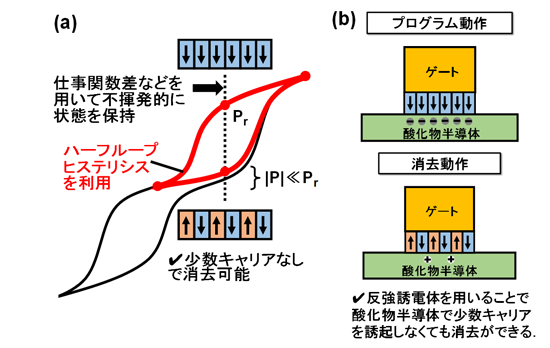

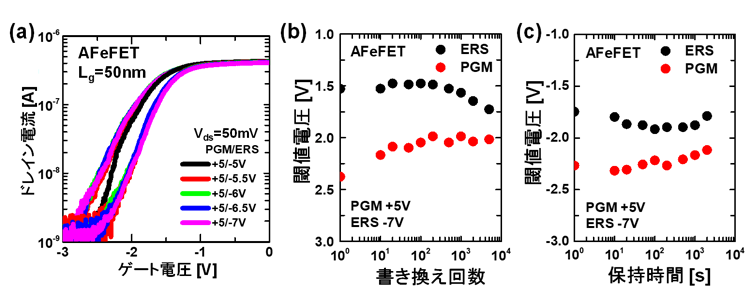

そこで、東京大学 生産技術研究所の小林 正治 准教授と奈良先端科学技術大学院大学の浦岡 行治 教授らの共同研究グループは、酸化物半導体であるIn2O3を従来のスパッタ法に代わるALD法で成膜する技術を開発しました。ALD法で成膜したIn2O3を用いて作製した薄膜トランジスタでは40cm2/Vsを超える高い移動度を示しました。そしてALD法によりIn2O3が三次元構造に均一に成膜することに成功しました。この成膜技術を用いて、同じくALD法で成膜できる二酸化ハフニウムジルコニウム(HfZrO2)強誘電体をゲート絶縁膜とするFeFETを試作し(図2)、理論的に予測した通り、1.5V程度のメモリウィンドウ(閾値電圧差)、104回を超える書き換え耐性、103秒を超える保持特性を実証しました(図3)。今回さらに反強誘電体ZrO2をゲート絶縁膜とする反強誘電体トランジスタ(AFeFET)を提案しました(図4)。酸化物半導体はN型半導体であり、多数キャリアである電子を誘起しやすい一方、少数キャリアである正孔を誘起しづらいことにより、プログラム状態に対して消去状態の保持特性が劣化しやすい特徴があります。反強誘電体を用いることで、少数キャリアを誘起しなくても効率的に消去動作が可能となり、消去状態の保持特性を改善できます。実際、0.7V程度のメモリウィンドウ、104回を超える書き換え耐性、103秒を超える保持特性を実証しました(図5)。本メモリデバイス技術は高密度かつ低消費電力であるため、IoTデバイスのストレージメモリに用いることで、ビッグデータを利活用する社会サービスの展開が期待されます。

<今後の展開>

本研究ではALD法でIn2O3を成膜しましたが、今後は多元素系酸化物半導体をALD法で成膜する技術を継続して進めていき、高移動度かつ高信頼性な酸化物半導体の三次元構造への均一な成膜を目指します。また、三次元積層数を増やして集積数を上げ高密度化を目指します。さらに、実用的な書き換え速度の実証に向けて、ゲート、ソース、ドレインでの寄生抵抗を減らした設計とプロセスインテグレーションを行います。

本研究は、JST知財活用支援事業スーパーハイウェイ支援を受けたものです。

○発表学会:

学会名:「2022 IEEE Silicon Nanoelectronics Workshop」

論文タイトル:A Vertical Channel Ferroelectric/Anti-Ferroelectric FET with ALD InOx and Field-Induced Polar-Axis Alignment for 3D High-Density Memory

著者:Zhuo Li*, Jixuan Wu, Xiaoran Mei, Xingyu Huang, Takuya Saraya, Toshiro Hiramoto, Takanori Takahashi, Mutsunori Uenuma, Yukiharu Uraoka*, and Masaharu Kobayashi*

学会URL:https://snw2022.conf.nycu.edu.tw/

○問い合わせ先:

東京大学 生産技術研究所

准教授 小林 正治(こばやし まさはる)

奈良先端科学技術大学院大学 先端科学技術研究科 物質創成科学領域

教授 浦岡 行治(うらおか ゆきはる)

○用語解説:

(注1)NANDフラッシュメモリ

半導体トランジスタのゲート絶縁膜の部分に電荷を保持できる層を形成することでメモリとして動作させることができるデバイス。ゲート電圧を印加して電荷保持層に注入(または放出)した電荷の量に応じてトランジスタの閾値電圧を変化させ、不揮発的に保持することができる。一般的にゲートに正の電圧を印加してデータを書き込むことをプログラム動作と呼び、ゲートに負の電圧を印加してデータを書き込むことを消去動作と呼ぶ。特に、そのトランジスタをソースとドレインを共有するように直列に接続させ高密度化させたものをNANDフラッシュメモリと呼ぶ。低コストで大容量なストレージとして従来のハードディスクドライブを置き換えつつある。現在は平面型のデバイス構造から、トランジスタを垂直方向に積層してチャネルを垂直に形成する三次元垂直チャネル構造をとって、さらなる高密度化を実現している。

(注2)強誘電体トランジスタ(FeFET)

半導体トランジスタのゲート絶縁膜の部分に強誘電体薄膜を形成することで、メモリとして動作させることができるデバイス。ゲート電圧を印加して強誘電体の自発分極の向きを反転(または維持)し、その向きに応じてトランジスタの閾値電圧を変化させ、不揮発的に保持することができる。一般的にゲートに正の電圧を印加してデータを書き込むことをプログラム動作と呼び、ゲートに負の電圧を印加してデータを書き込むことを消去動作と呼ぶ。強誘電体は比較的低い電圧で書き換えが可能であるため、低消費電力な書き換え動作が可能である。

(注3)酸化物半導体

半導体としてよく知られるのがシリコンであるが、金属系の酸化物の中にも半導体の性質を示すものが知られている。その代表がIGZO(InGaZnO)であり、シリコンに比べて大きなバンドギャップを有し、スパッタで高移動度かつ高信頼性な薄膜を低温で成膜可能なことから、フラットパネルディスプレイの駆動トランジスタなどに用いられている。

(注4)スパッタ法

スパッタ法は、二つの電極それぞれの上に成膜材料のターゲットと成膜される基板を設置し、その間にアルゴン等の希ガスを導入し、大電圧を印加してプラズマを生成し、その中で形成されるバイアス電圧によって希ガスの陽イオンをターゲットに打ち込み、その反動でターゲットから出てくる材料物質が基板上に堆積されることで成膜する方法である。材料物質は直進性をもって基板上に成膜され、かつ表面拡散が小さいため、平面上には均一に成膜できる一方、立体構造物への均一な成膜は一般的に難しい。

(注5)原子層堆積(ALD)法

原子層堆積法は、従来の化学気相成長法の一種であり、反応プリカーサをパルス状に短時間チャンバーに供給し、成膜するウェハ上に単分子層飽和させ、次に酸化剤となる水や酸素などをパルス状に短時間供給し、飽和された分子層を酸化して原子層の酸化物を形成する。この過程を繰り返すことで原子層毎に成膜することができる方法である。平面での成膜はもとより三次元構造でも、ローディング効果が小さく均一な成膜ができることが特長である。

(注6)反強誘電体

強誘電体は電界によって自発分極の向きを一斉に上下どちらか一方に配向させて大きな分極状態を形成する。対して反強誘電体は、大きな電界を印加している場合には強誘電体と基本的に同じ分極状態を形成するが、電界を印加していない場合には自発分極が互いに逆向きを向いて実質的に分極が無い状態を形成する材料である。分極電荷と電圧の関係は、強誘電体では1つのヒステリシスループとなるのに対して反強誘電体では2つのヒステリシスループが結合したものになる。

○添付資料:

図1 (a)提案している酸化物半導体をチャネルとした三次元垂直チャネル型FeFETの模式図。ゲート絶縁膜には強誘電体HfO2を用いる。(b)酸化物半導体を三次元構造に成膜するときの問題と解決法。ALD法を用いることで三次元構造に均一に成膜できる。

図2 (a)試作した三次元垂直チャネル型FeFETの断面透過型電子顕微鏡(TEM)写真。強誘電体HfO2と酸化物半導体であるIn2O3がともに均一に成膜されている。(b)試作したプロトタイプデバイス全体の断面模式図。

図3 試作した三次元垂直チャネル型FeFETの(a)ドレイン電流-ゲート電圧特性、(b)プログラム(PGM)パルス電圧と消去(ERS)パルス電圧を交互に印加していった時のFeFETの閾値変動を表す書き換え耐性、(c)PGMまたはERSパルス電圧を印加した後のFeFETの閾値電圧の安定性を表す保持特性。1.5V以上のメモリウィンドウ、104回以上の書き換え耐性、103秒以上の保持特性が得られた。

図4 AFeFETの有効性を説明する概念図。(a)反強誘電体のハーフループヒステリシスを強誘電体ヒステリシスと同じように用いる。(b)反強誘電体のハーフループヒステリシスを用いることで、酸化物半導体が少数キャリアを誘起しなくても効率的に消去動作ができる。

図5 試作した三次元垂直チャネル型AFeFETの(a)ドレイン電流-ゲート電圧特性、(b)プログラム(PGM)パルス電圧と消去(ERS)パルス電圧を交互に印加していった時のAFeFETの閾値変動を表す書き換え耐性、(c)PGMまたはERSパルス電圧を印加した後のAFeFETの閾値電圧の安定性を表す保持特性。0.7V以上のメモリウィンドウ、104回以上の書き換え耐性、103秒以上の保持特性が得られた。