2022-04-07 カリフォルニア大学バークレー校(UCB)

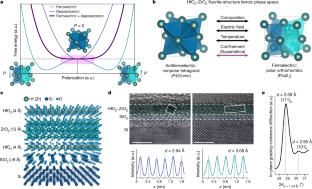

・この効率アップは、物質に電荷を蓄えるために必要な電圧の量を減らすことができる「負の容量」と呼ばれる効果によって実現されています。サラハディンは2008年に負の容量の存在を理論的に予言し、2011年に強誘電体結晶で初めてこの効果を実証しました。・今回の研究では、酸化ハフニウムと酸化ジルコニウムを層状に積み重ねた人工結晶で負の静電容量を実現し、先進的なシリコントランジスターと容易に整合することを示した。この材料をモデルトランジスタに組み込むことで、負の静電容量効果によりトランジスタの制御に必要な電圧量を大幅に低減し、その結果、コンピュータが消費するエネルギー量を低減できることが実証された。

<関連情報>

- https://news.berkeley.edu/2022/04/07/engineered-crystals-could-help-computers-run-on-less-power/

- https://www.nature.com/articles/s41586-022-04425-6

先端トランジスタ用超薄膜強磁性体HfO2-ZrO2超格子ゲートスタック Ultrathin ferroic HfO2–ZrO2 superlattice gate stack for advanced transistors

Suraj S. Cheem>,Nirmaan Shanker,Li-Chen Wang,Cheng-Hsiang Hsu,Shang-Lin Hsu,Yu-Hung Liao,Matthew San Jose,Jorge Gomez,Wriddhi Chakraborty,Wenshen Li,Jong-Ho Bae,Steve K. Volkman,Daewoong Kwon,Yoonsoo Rho,Gianni Pinelli,Ravi Rastogi,Dominick Pipitone,Corey Stull,Matthew Cook,Brian Tyrrell,Vladimir A. Stoica,Zhan Zhang,John W. Freeland,Christopher J. Tassone,Apurva Mehta,Ghazal Saheli,David Thompson,Dong Ik Suh,Won-Tae Koo,Kab-Jin Nam,Dong Jin Jung,Woo-Bin Song,Chung-Hsun Lin,Seunggeol Nam,Jinseong Heo,Narendra Parihar,Costas P. Grigoropoulos,Padraic Shafer,Patrick Fay,Ramamoorthy Ramesh,Souvik Mahapatra,Jim Ciston,Suman Datta,Mohamed Mohamed,Chenming Hu &Sayeef Salahuddin

Nature Published: 06 April 2022

Abstract

With the scaling of lateral dimensions in advanced transistors, an increased gate capacitance is desirable both to retain the control of the gate electrode over the channel and to reduce the operating voltage1. This led to a fundamental change in the gate stack in 2008, the incorporation of high-dielectric-constant HfO2 (ref. 2), which remains the material of choice to date. Here we report HfO2–ZrO2 superlattice heterostructures as a gate stack, stabilized with mixed ferroelectric–antiferroelectric order, directly integrated onto Si transistors, and scaled down to approximately 20 ångströms, the same gate oxide thickness required for high-performance transistors. The overall equivalent oxide thickness in metal–oxide–semiconductor capacitors is equivalent to an effective SiO2 thickness of approximately 6.5 ångströms. Such a low effective oxide thickness and the resulting large capacitance cannot be achieved in conventional HfO2-based high-dielectric-constant gate stacks without scavenging the interfacial SiO2, which has adverse effects on the electron transport and gate leakage current3. Accordingly, our gate stacks, which do not require such scavenging, provide substantially lower leakage current and no mobility degradation. This work demonstrates that ultrathin ferroic HfO2–ZrO2 multilayers, stabilized with competing ferroelectric–antiferroelectric order in the two-nanometre-thickness regime, provide a path towards advanced gate oxide stacks in electronic devices beyond conventional HfO2-based high-dielectric-constant materials.