2020-02-27 産業技術総合研究所

ポイント

- プロセスデザインキット(PDK)を整備し、ユーザーによるデバイス設計が容易に

- 将来の光デバイス製造の研究開発エコシステムを構築

- シリコンフォトニクスデバイスの多様な応用にむけた開発を加速

概要

国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)電子光技術研究部門【研究部門長 森 雅彦】とTIA推進センター【センター長 金丸 正剛】は、産総研で開発した世界最先端のシリコンフォトニクス技術を普及させるため、産総研以外の幅広いユーザーが利用可能な国内初のシリコンフォトニクスデバイスの試作体制を構築した。この試作体制は、加工精度に優れる300 mmウエハープロセスを利用した研究開発用公的シリコンフォトニクス試作体制としては世界で唯一である。

技術面では、これまで産総研で独自に開発してきたシリコンフォトニクス技術を基にデバイス設計基本情報や標準デバイスメニューをまとめたプロセスデザインキット(PDK)を整備し、ユーザーによるデバイス設計を容易にした。また、運用面としては、産総研コンソーシアムであるシリコンフォトニクスコンソーシアムの活動の一環として、設計情報の集約や試作デバイスの分配などを行うユーザー窓口機能を設置し、利便性の良い試作体制を構築した。2019年10月には、コンソーシアムの参加企業や大学をユーザーとした1回目の相乗り試作を完了し、今回構築した研究開発試作体制の良好な機能が確認された。今後、国内外の民間企業・大学などに研究開発試作を幅広く提供し、開発技術の普及に努めていく。

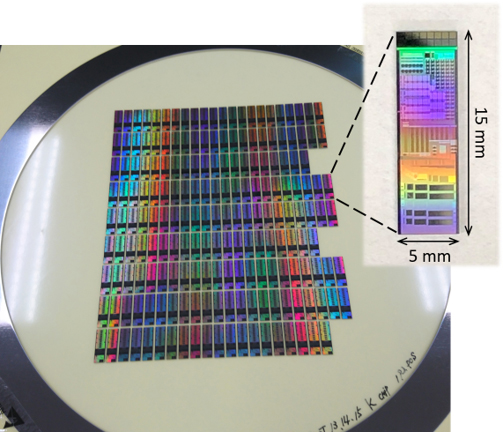

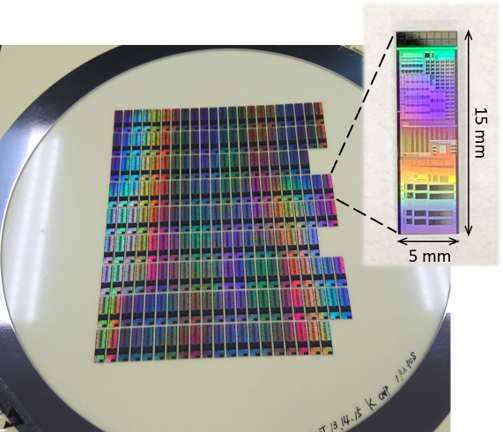

2019年度相乗り試作においてユーザーに提供したシリコンフォトニクスチップ

成果普及の社会的背景

最近、産業界において、シリコンフォトニクス技術に対する関心が高まっている。シリコンフォトニクス技術は、量産性、経済性、微細加工性に優れるシリコン電子回路の製造技術をベースとした、超小型光デバイスの製造技術であり、ポストムーア時代において、IoTや5Gなどの将来の情報通信システムで必要とされている安価で高集積化された光デバイスの量産を可能とする技術として期待されている。シリコンフォトニクス技術は従来の光デバイス技術に比べけた違いの量産能力を持つが、それに必要な大規模な製造設備を光デバイスメーカーが保有することは困難であり、シリコンフォトニクス技術の普及には、その研究開発でもシリコン電子回路と同様の、設計と製造を分離したエコシステムを構築する必要があった。

技術の内容

産総研は、国内では最先端のシリコンデバイスの公的研究開発施設であるTIA推進センターのスーパークリーンルーム産学官連携研究棟(SCR)を活用して、シリコンフォトニクス技術の研究開発に取り組んできた。加工精度に優れる300 mmウエハープロセスを利用し、世界で最も低損失の光導波路、世界最大規模の光マトリックススイッチ、さらには高速変調器などさまざまな光デバイスを実現しており、世界最高水準のシリコンフォトニクス技術となっている。

成果普及の内容

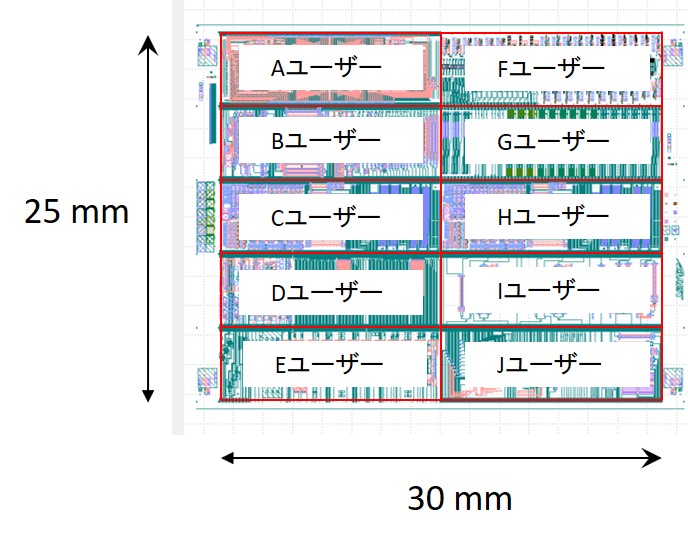

これまで産総研で開発してきたシリコンフォトニクス技術を基にデバイス設計基本情報や標準デバイスメニューをまとめたPDKを整備し、産総研コンソーシアムであるシリコンフォトニクスコンソーシアムで、試作を希望するユーザーに開示した。ユーザーはこのPDKに基づいて設計を行うため、製造技術の詳細を知る必要がない。また、コンソーシアム参加企業の協力を得て、設計情報の集約や試作デバイスの分配などを行うユーザー窓口機能を設置し、利便性の良い運用体制も整えた。このような技術、運用両面における試作体制を構築した後、2019年5月より複数ユーザー相乗り試作を実施し、2019年9月に第1回のウエハー試作を完了、10月に各ユーザーにシリコンフォトニクスデバイスチップの提供を完了した。図1に今回の相乗り試作のチップのイメージを示す。現在、各ユーザーによりそれぞれのデバイス評価が進められており、一部のユーザーから既に良好なフィードバックを得ている。以上により、今回構築した試作体制が、研究開発用シリコンフォトニクス設計、製造のエコシステムとして機能することが確認され、幅広く外部ユーザーに提供できる体制が整った。なお、この試作体制は加工精度に優れる300 mmウエハープロセスを利用した世界で唯一の研究開発用公的シリコンフォトニクス試作体制である。

25 x 30 mmのユーザー試作領域の中にユーザーごとに5 x 15 mmサイズの専用チップを配置して、まとめて一括製造した。

今後の予定

最新のシリコンフォトニクス技術の開発を継続し、開発技術を順次PDKに反映することにより、常に最新技術を提供できる試作体制を整備していく。また、国内外のユーザーに研究開発試作を幅広く提供し、開発技術の普及に努めていく。

用語の説明

- ◆シリコンフォトニクス

- シリコン電子回路の製造に用いる相補型金属酸化膜半導体(CMOS)製造技術と設備を使って、光デバイスを製造する技術。安価で高集積化された光デバイスの量産を可能とする技術として期待されている。

- ◆デバイス設計基本情報

- 特定のウエハープロセスの製造ラインで実現可能な寸法や材料のさまざまな特性をまとめたもの。

- ◆標準デバイスメニュー

- 特定のウエハープロセスの製造ラインで標準的に製造可能なデバイスのリスト。

- ◆プロセスデザインキット(PDK)

- 半導体デバイスを特定のウエハープロセスの製造ラインで作製するにあたって、デバイス設計基本情報や標準デバイスメニューなどのデバイス設計に必要な情報をまとめたもの。

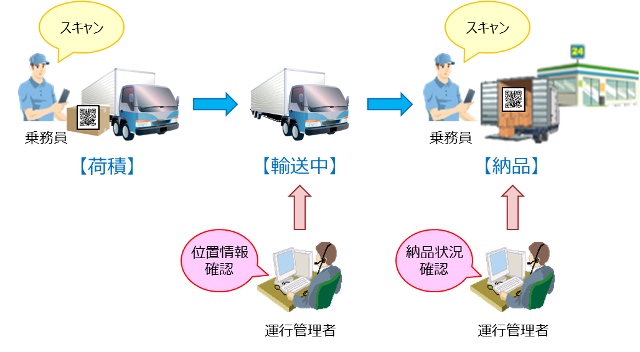

- ◆相乗り試作

- 複数のユーザーが1枚のウエハーに相乗りして半導体デバイスの製造を行う方法。試作費用を1/5~1/10に抑えることが可能になる。ユーザーごとに専用チップ領域を配置して、まとめて一括製造を行う。ユーザーには各ユーザー専用のチップのみが送付され、他ユーザーの試作内容を知ることができない体制で製造が行われる。

- ◆ポストムーア時代

- 半導体技術の進展を支えていた微細化技術が物理的な限界に到達し、半導体チップの性能が1~2年の間にほぼ倍増するという「ムーアの法則」が適用できなくなった後の時代を指す。 これまでの微細化による半導体チップの性能が望めなくなるため、より高性能な情報通信システムを実現するには、半導体微細化以外の新しい技術を導入していく必要がある。

- ◆エコシステム

- 主に情報通信産業において、本来の生物群の循環系という元の意味から転化して、企業間の協業・分業・連携による製造体系をさす。例として、設計、半導体チップ、内蔵カメラ、表示デバイス、組み立て、など、多くの企業の協業・分業・連携により製造されるスマートフォンの製造エコシステムが有名である。

- ◆スーパークリーンルーム産学官連携研究棟(SCR)

- TIA推進センターの運用する共用施設の一つ。3,000 m2のクラス3クリーンルームに、300 mmウエハー用半導体プロセス装置をそろえている。既存のプロセスメニューを活用した研究開発や個々のプロセスや単独処理などを行うことができる。