メモリーデバイスの低消費電力化、高速化、大容量化に期待

2019-06-10 東京大学

ポイント

◆シリコンチャネルでは誘電率の低い界面層が形成されてしまい、低電圧動作が難しく信頼性が低いことが問題だった。

◆極薄の金属酸化物半導体IGZOをチャネルとして、スイッチング特性に優れた高移動度なトランジスター型強誘電体メモリーの開発に成功した。

◆この技術によりIoTデバイスのエネルギー効率が飛躍的に向上し、より高度で充実したネットワーク、サービスの展開が期待される。

概要

JST 戦略的創造研究推進事業において、東京大学 生産技術研究所の小林 正治 准教授らは、8ナノメートル(nm)の金属酸化物半導体IGZO注1)をチャネルとしたトランジスター型強誘電体メモリー(FeFET)注2)の開発に成功しました。本技術により、サブスレッショルド係数注3)は理想的な60ミリボルト/デック(mV/dec)、メモリーウィンドウは0.5ボルト(V)以上の高移動度で低電圧動作可能な優れたメモリー特性を実現しました。

強誘電体二酸化ハフニウム(HfO2)注4)をゲート絶縁膜としたFeFETは、低消費電力で大容量なメモリーデバイスとして注目を集めていますが、シリコンをチャネルとするデバイス構造の場合、誘電率の低い界面層が形成されてしまい、界面層への電圧降下と電荷トラップが起こるため低電圧動作と高信頼性動作を同時に実現することが困難でした。

本研究では、界面層の形成と電荷トラップの影響を抑制し、3次元積層構造でも高い読み出し電流を得るために、金属酸化物半導体IGZOをチャネルとする強誘電体HfO2ゲート絶縁膜FeFETを提案しました。このデバイス構造を用いると、IGZOと強誘電体HfO2の間で誘電率の低い界面層の形成を抑えることができます。

本成果は低消費電力で大容量、かつ高速なメモリーデバイスの新しい可能性を拓き、IoTエッジデバイスのエネルギー効率の飛躍的な向上や高度なIoTネットワークの展開、そしてビッグデータに基づく社会サービスの充実が期待されます。

本研究成果は、2019年6月11日(日本時間)に「VLSI Technology Symposium 2019」で発表されます。

<研究の背景と経緯>

全ての「もの」や「こと」がインターネットを通じてつながったIoT社会の実現に向けて、センサーや通信機能が備わったセンサーノードデバイスが重要な役割を担い、今後数兆個以上導入されることが試算されています。そのようなIoTデバイスは、低消費電力であることが必然的に求められ、消費電力で支配的となるリーク電力(電流の漏れ出し)を削減するためにはメモリーの待機時の電力を抑えることができる低消費電力な不揮発性メモリーが必要となります。

強誘電体をゲート絶縁膜とするトランジスター型強誘電体メモリー(FeFET)は、低消費電力で大容量なメモリーデバイスという特徴があります。特に集積回路作製プロセスと整合性が高く、10nm以下の膜厚でも強誘電性を示す強誘電体二酸化ハフニウム(HfO2)材料が開発され、注目を集めています。さらにフラッシュメモリーのような3次元積層構造をとることも期待されており、IoTデバイスに限らず、サーバー用の超大容量なメモリーとしての潜在能力も予見されています。

しかし、シリコンをチャネルとする従来のFeFETのデバイス構造では、ゲート絶縁膜とシリコンチャネルの間に誘電率の低い界面層が形成され、界面層に大きな電圧降下や界面層を通じて電荷トラップが起こり、低電圧動作と高信頼性動作を同時に実現することが困難でした。また、3次元積層構造にする場合にはチャネルは移動度の低いポリシリコンを用いる必要があるため読み出し電流が小さく、アクセス時間が遅くなることが懸念されていました。

<研究の背景と経緯>

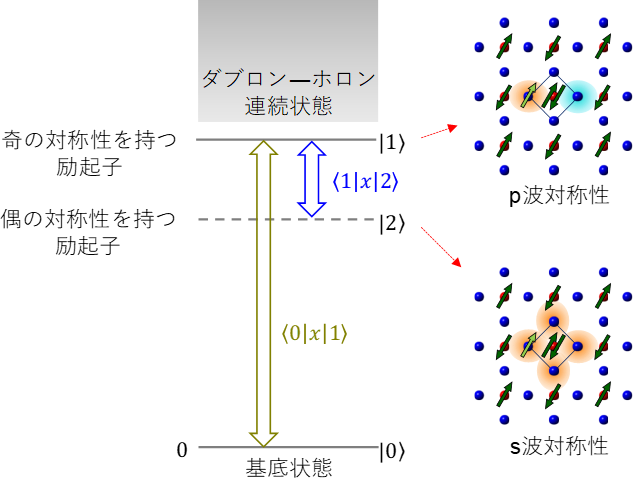

本研究では、界面層の形成と電荷トラップの影響を抑制し、3次元積層構造でも高い読み出し電流を得るために、金属酸化物半導体IGZOをチャネルとする強誘電体HfO2ゲート絶縁膜FeFETを提案しました。このデバイス構造を用いると、IGZO自体が金属酸化膜であるため、強誘電体HfO2との間で誘電率の低い界面層の形成を抑えることができます(図1)。さらにN型にドープされているIGZOをチャネルにすることでジャンクションレストランジスター注5)として動作し、キャリヤーは界面でなくボディ(チャネル中央部)を流れるため、キャリヤーの電荷トランプを抑制することが可能です。ジャンクションレストランジスターがノーマリーオフ動作、つまりゲート電圧がゼロの時に電流が流れないようにするには閾値電圧を制御する必要があり、IGZOの膜厚を10nm以下にしました。10nm以下の膜厚では、ポリシリコンの移動度は10平方センチメートル/ボルトセック(cm2/Vs)よりも低くなってしまいますが、IGZOであれば10~100cm2/Vsの高い移動度を維持することができます。

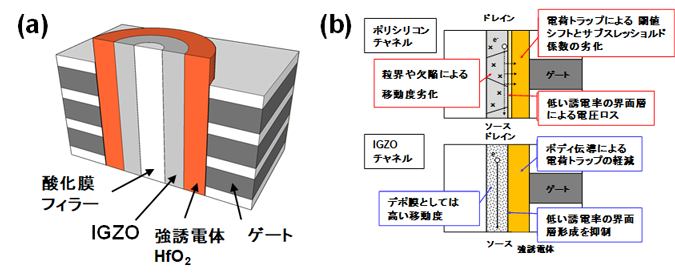

デバイスプロセスの開発ではまず、IGZOの膜厚の最適化を行いました。IGZOをチャネルとし、二酸化ケイ素(SiO2)をゲート絶縁膜とする通常のMOSFETを作製してサブスレッショルド係数と閾値電圧の膜厚依存性を調査したところ、膜厚を薄くするにつれてサブスレッショルド係数が小さくなり、閾値も負から正に変化することが分かりました(図2)。最終的に8nmの膜厚が最適値となり、サブスレッショルド係数は理想的な60mV/decで、閾値電圧も正となりノーマリーオフ動作することが分かりました。

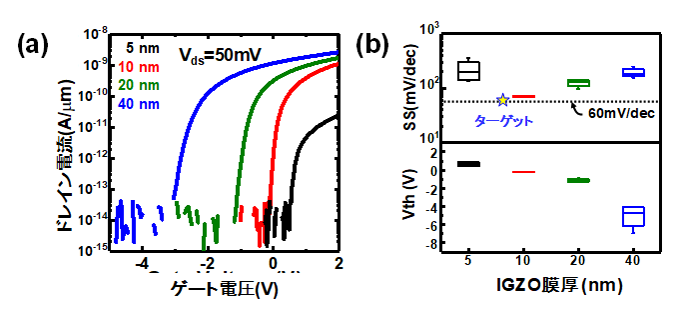

次にIGZOをチャネルとした場合に、ゲート絶縁膜であるHfO2が強誘電性を示すかを調査しました。上部電極をTiN、下部電極をIGZOとして、Zrを添加したHfO2(HfZrO2)のキャパシターを作製し評価しました(図3)。断面TEM像から分かるように界面層は形成されておらず(図3(a))、また強誘電体の特徴を示す残留分極は30マイクロクーロン/平方センチメートル(μC/cm2)と極めて大きな値を示し(図3(b))、IGZOチャネル上に強誘電体HfO2が形成できることを明らかにしました。

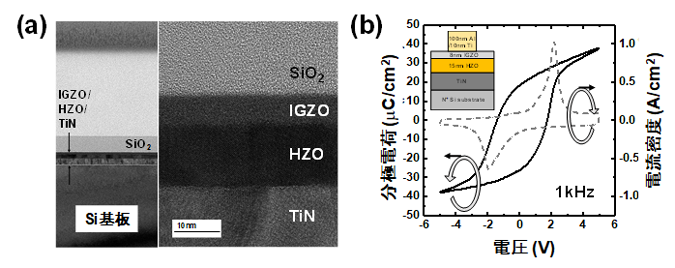

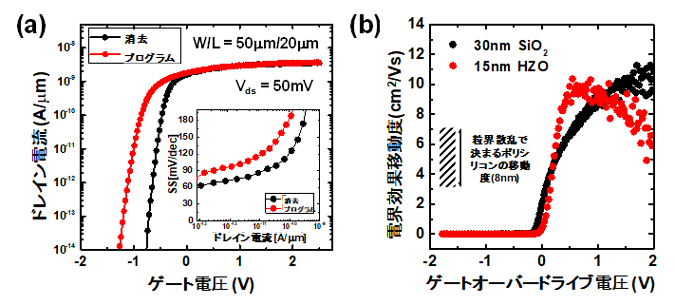

以上のプロセス要素を用いて、8nmの膜厚のIGZOをチャネルとする強誘電体HfO2ゲート絶縁膜FeFETを作製しました(図4)。電流伝達特性は電流のオンオフ比が5桁以上の良好な特性を示し(図4(a))、サブスレッショルド係数はMOSFETで得られた結果と約60mV/decという急峻な特性を得ることができました。さらに電界効果移動度を測定したところ10cm2/Vs以上の値が得られ、これは同じ膜厚でのポリシリコンチャネルより50パーセント以上高い値となります(図4(b))。

シリコンではない新材料チャネルをメモリーに応用してFeFETの低電圧動作や高信頼性動作、高移動度を実現したことにより、新たなメモリーデバイス開発の方向性を示し、さらなる低消費電力化、大容量化、高速化の可能性を拓いたといえます。

<今後の展開>

本研究ではIGZOをチャネルとするFeFETのコンセプト実証のため、バックゲート型のデバイス構造を採用しました。今後はトップゲート型、3次元積層型構造の場合には積層型ゲート構造を開発、評価する必要があります。また、保持特性を向上させるためには強誘電体HfO2ゲート絶縁膜の材料特性を調整し、IoTやストレージクラスメモリーへの応用のため、1.8V動作や書き換え速度の高速化、10年間のデータ保持、1012回の書き換え耐性、1~10マイクロアンペアなどの読み出し電流を目指してデバイス開発を行っていきます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

戦略的創造研究推進事業 個人型研究(さきがけ)

研究領域:「素材・デバイス・システム融合による革新的ナノエレクトロニクスの創成」

(研究総括:桜井 貴康 東京大学 生産技術研究所 教授(研究当時))

研究課題名:「超低消費電力動作に向けたゲート絶縁膜の負性容量による急峻スロープトランジスタ技術の開発とナノワイヤ構造への応用」

研 究 者:小林 正治(東京大学 生産技術研究所 准教授)

研究実施場所:東京大学 生産技術研究所

研究期間:平成27年10月~平成31年3月

<参考図>

図1

(a)提案する3次元積層型IGZOチャネル強誘電体HfO2 FeFETの模式図、(b)ポリシリコンチャネルとIGZOチャネルのFeFETの特徴比較。IGZOチャネルを用いることで、界面層形成を抑制でき、電荷トラップを抑え、高移動度を実現できる。

図2

(a)FeFET開発のための準備段階として作製したSiO2をゲート絶縁膜とするMOSFETの電流伝達特性、(b)(a)のデータからサブスレッショルド係数と閾値電圧を抽出した。膜厚が薄いほどサブスレッショルド係数が急峻で閾値電圧も正となる。本研究では8nmをターゲットの膜厚とした。

図3

(a)作製したTiN/HfZrO2/IGZOキャパシターの断面TEM像、(b)キャパシターの分極電荷および電流密度特性。低い誘電率の界面層の形成が抑制され、IGZO上に強誘電体HfO2が形成できることが確認された。

図4

(a)作製したIGZOチャネルFeFETの電流伝達特性、(b)電界効果移動度。ほぼ理想的なサブスレッショルド係数である60mV/decを持ち、0.5V以上の大きなメモリーウィンドウを持つFeFETを実現。電界効果移動度もFeFET構造で10cm2/Vs以上の値が得られ、同じ膜厚でのポリシリコンの移動度を上回る。

<用語解説>

注1)金属酸化物半導体IGZO

シリコンやガリウムヒ素を始めとする代表的な半導体は、IV族またはIII-V族の元素を用いたものが多いが、近年、金属酸化物で半導体の性質を示す材料が注目を集めている。金属酸化物半導体は一般に、成膜プロセスが容易でありバンドギャップが広いものが多い、といった特徴を持つ。IGZOはIn-Ga-Zn-Oからなる材料で、アモルファス状態で半導体となり、移動度が10~100cm2/Vsを示し、現在ディスプレイのドライバ回路などで使われている。

注2)トランジスター型強誘電体メモリー(FeFET)

強誘電体メモリーにはさまざまなデバイス構造が存在する。トランジスター型強誘電体メモリーとは、通常のトランジスター構造のゲート絶縁膜を強誘電体薄膜で置き換え、この強誘電体ゲート絶縁膜中の自発分極の向きによってトランジスターの閾値を高くしたり低くしたりすることでメモリー特性を実現するデバイスである。

注3)サブスレッショルド係数

電界効果トランジスターでは、閾値(スレッショルド:Threshold)電圧より低いゲート電圧領域をサブスレッショルド領域と呼び、電流は拡散電流に支配され電流はゲート電圧の変化に対して指数関数的に変化する。この領域で電流が一桁増大するために必要なゲート電圧の増加量をサブスレッショルド係数と呼ぶ。

注4)強誘電体二酸化ハフニウム(HfO2)

強誘電体とは、電界をかけることで形成した分極が、電界をかけなくても自発分極として維持され、その向きを印加する電界の向きで制御することができる材料である。この性質を利用してさまざまなメモリーデバイスへ応用されている。従来はペロブスカイト構造の強誘電体が用いられてきたが、高すぎる誘電率や加工の難しさや材料の信頼性など問題があった。近年集積回路作製プロセスと整合性の高いHfO2材料で強誘電性が発見され、この材料を用いたメモリーデバイスの研究が盛んになっている。

注5)ジャンクションレストランジスター

N型のMOSトランジスターでは、基板はP型で、ソースとドレインはN型となるようにデバイスを形成する。そのため基板とソース・ドレインの間にはPN接合(ジャンクション)が形成され、MOSトランジスターはチャネルとゲート絶縁膜の界面に少数キャリヤーによる反転層を形成して電流を流す。一方N型のジャンクションレストランジスターは基板を高濃度のN形にするだけで、基板とソース・ドレインで別々の型にはせずPN接合を形成しない。電流は主に多数キャリヤーが基板(ボディ)を流れることで生じる。

<発表情報>

タイトル:”Experimental Demonstration of Ferroelectric HfO2 FET with Ultrathin-body IGZO for High-Density and Low-Power Memory Application”

(大容量で低消費電力な極薄IGZOチャネルを有する強誘電体HfO2トランジスターメモリの実験実証)

発表日時:2019年6月11日(火) 午後2時50分~

開催場所:リーガロイヤルホテル京都

<お問い合わせ先>

<研究に関すること>

小林 正治(コバヤシ マサハル)

東京大学 生産技術研究所 准教授

<JST事業に関すること>

中村 幹(ナカムラ ツヨシ)

科学技術振興機構 戦略研究推進部 グリーンイノベーショングループ