2023-04-03 マサチューセッツ大学アマースト校

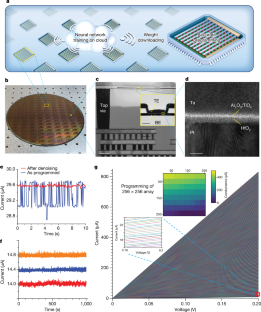

これは、どのタイプの記憶装置よりも多いという。今後、この技術は、低電力かつ高スループットなエッジAIアプリケーションだけでなく、科学計算などの高精度なアプリケーションにも応用されることが期待される。

<関連情報>

- https://www.umass.edu/news/article/pioneering-research-qiangfei-xia-memristors-pushes-frontier-artificial-intelligence

- https://www.nature.com/articles/s41586-023-05759-5

CMOSに集積されたメモリスタの数千のコンダクタンスレベル Thousands of conductance levels in memristors integrated on CMOS

Mingyi Rao,Hao Tang,Jiangbin Wu,Wenhao Song,Max Zhang,Wenbo Yin,Ye Zhuo,Fatemeh Kiani,Benjamin Chen,Xiangqi Jiang,Hefei Liu,Hung-Yu Chen,Rivu Midya,Fan Ye,Hao Jiang,Zhongrui Wang,Mingche Wu,Miao Hu,Han Wang,Qiangfei Xia,Ning Ge,Ju Li & J. Joshua Yang

Nature Published:29 March 2023

DOI:https://doi.org/10.1038/s41586-023-05759-5

Abstract

Neural networks based on memristive devices1,2,3 have the ability to improve throughput and energy efficiency for machine learning4,5 and artificial intelligence6, especially in edge applications7,8,9,10,11,12,13,14,15,16,17,18,19,20,21. Because training a neural network model from scratch is costly in terms of hardware resources, time and energy, it is impractical to do it individually on billions of memristive neural networks distributed at the edge. A practical approach would be to download the synaptic weights obtained from the cloud training and program them directly into memristors for the commercialization of edge applications. Some post-tuning in memristor conductance could be done afterwards or during applications to adapt to specific situations. Therefore, in neural network applications, memristors require high-precision programmability to guarantee uniform and accurate performance across a large number of memristive networks22,23,24,25,26,27,28. This requires many distinguishable conductance levels on each memristive device, not only laboratory-made devices but also devices fabricated in factories. Analog memristors with many conductance states also benefit other applications, such as neural network training, scientific computing and even ‘mortal computing’25,29,30. Here we report 2,048 conductance levels achieved with memristors in fully integrated chips with 256 × 256 memristor arrays monolithically integrated on complementary metal–oxide–semiconductor (CMOS) circuits in a commercial foundry. We have identified the underlying physics that previously limited the number of conductance levels that could be achieved in memristors and developed electrical operation protocols to avoid such limitations. These results provide insights into the fundamental understanding of the microscopic picture of memristive switching as well as approaches to enable high-precision memristors for various applications.