2025-03-19 カリフォルニア大学サンタバーバラ校 (UCSB)

<関連情報>

- https://news.ucsb.edu/2025/021805/next-gen-3d-transistors-transform-energy-efficient-electronics

- https://www.nature.com/articles/s41928-024-01289-8

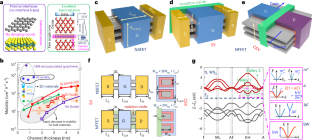

将来のCMOS微細化のための2次元半導体を用いた3次元トランジスタ Three-dimensional transistors with two-dimensional semiconductors for future CMOS scaling

Arnab Pal,Tanmay Chavan,Jacob Jabbour,Wei Cao & Kaustav Banerjee

Nature Electronics Published:16 December 2024

DOI:https://doi.org/10.1038/s41928-024-01289-8

Abstract

Atomically thin two-dimensional (2D) semiconductors—particularly transition metal dichalcogenides—are potential channel materials for post-silicon complementary metal–oxide–semiconductor (CMOS) field-effect transistors. However, their application in CMOS technology will require implementation in three-dimensional (3D) transistors. Here we report a framework for designing scaled 3D transistors using 2D semiconductors. Our approach is based on non-equilibrium Green’s function quantum transport simulations that incorporate the effects of non-ideal Schottky contacts and inclusive capacitance calculations, with material inputs derived from density functional theory simulations. A comparative performance analysis of different 3D transistors (2D and silicon based) and channel thicknesses is carried out for both low-standby-power and high-performance applications. This suggests that trilayer tungsten disulfide is the most promising material, offering an improvement in energy–delay product of over 55% compared with silicon counterparts, potentially extending CMOS scaling down to a few nanometres. We also show that 2D semiconductors could be uniquely engineered to create 2D nanoplate field-effect transistors that offer nearly tenfold improvement in integration density and drive current over both 2D- and silicon-based 3D field-effect transistors with similar footprints.