2021-07-21 東京大学国際高等研究所

1. 発表者:

酒見 悠介 (東京大学 生産技術研究所 民間等共同研究員 (研究当時)/日本電気株式会社)

森野 佳生 (東京大学 生産技術研究所 特任助教 (研究当時)/九州大学 大学院総合理工学研究院 准教授)

森江 隆 (九州工業大学 大学院生命体工学研究科 教授/東京大学 生産技術研究所 リサーチフェロー(併任))

合原 一幸 (東京大学 特別教授・名誉教授/東京大学国際高等研究所ニューロインテリジェンス国際研究機構 副機構長)

2. 発表ポイント:

◆次世代人工知能として期待されているスパイキングニューラルネットワーク(注1)において、高い認識性能を示す教師ありアルゴリズムを開発した。

◆提案アルゴリズムは、スパイクのタイミングや順序を用いて情報処理する時間符号を用いており、少ないスパイク数で情報処理を行うことが出来るため低消費電力動作につながる。

◆さらに、本アルゴリズムは、アナログ集積回路実装を容易にするよう開発されているため、専用ハードウェアにより超低消費電力なシステムの構築が期待できる。

3.発表概要:

東京大学 生産技術研究所の酒見 悠介 民間等共同研究員(研究当時)、森野 佳生 特任助教(研究当時、現在:九州大学 准教授)、森江 隆 教授と合原 一幸 特別教授/名誉教授(東京大学国際高等研究所ニューロインテリジェンス国際研究機構 副機構長)らの研究チームは、超低消費電力回路実装に適した新しいスパイキングニューラルネットワークモデルを開発した(図1)。

この成果は、2021年7月19日にIEEE(アイ・トリプル・イー)の論文誌「IEEE Transactions on Neural Networks and Learning Systems」に速報オンライン版が掲載されました。

なお、本成果は本論文の投稿に先立ち、東京大学とNECから特許申請されている(発明の名称:ニューラルネットワーク装置、ニューラルネットワークシステム、処理方法およびプログラム 出願番号:特願2019-052880)。

本研究の一部は、日本電気株式会社(NEC)と東京大学との社会連携研究部門『ブレインモルフィックAIプロジェクト』の助成を受けたものである。

4.発表内容:

■ 背景

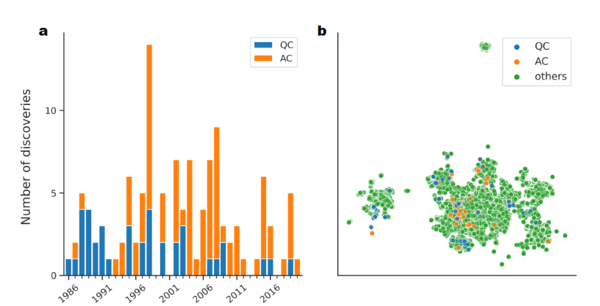

近年の深層学習の発展によって、物体認識、自然言語認識、計画立案、予測など、様々な複雑なタスクがデータからの学習で実現できるようになった。この技術を、医療や製造業、自動運転など、より広く社会に役立てるには、センシングデータの処理や、人間とAIとのインタラクションなどをリアルタイムに実行することが求められる。そのためには、データをクラウドに送らず、その場で処理することが重要となるが、深層学習は大きな電力を消費する大規模なシステムを必要とするため、あらゆる場所にそのようなシステムを構築することは難しい。そこでスマートフォンのような小規模なシステムにも搭載可能な、低消費電力な専用AIハードウェア(AIチップ)が、アメリカや中国を中心に盛んに開発されている。しかし、深層学習ベースのAIチップの低消費電力化は限界に近づいている。そこで、さらなる低消費電力化が可能な新しいニューラルネットワークモデルが望まれている。そのための一つの解決手段として、脳が省エネルギ―で高性能であることから、深層学習モデルよりも実際の脳への模倣度を進めた数理モデルであるスパイキングニューラルネットワーク(SNN)を用いた学習モデルが注目されている。

SNNは、ニューロンが非同期的に動作する特徴と、少数のスパイク信号により情報処理をする特徴を有しているため、専用AIチップで回路実装すると高い電力効率を示すと期待されている。しかし現状のSNNモデルは、少なくとも一般的な画像認識タスクでは深層学習に認識性能が及んでいない。また、上記のようなSNNの特徴を活用するためには、AIチップの回路設計の難易度が大幅に上がってしまうことが知られている。SNNを用いて低電力なシステムを構築するためには、回路実装の困難さを緩和し、同時に学習性能も向上させていく学習モデルが求められる。

■ 内容

我々は、高い電力効率を示すSNNを構築するため、専用AIチップでの実装を想定してモデルを構築するアプローチをとった。SNNは実際の神経細胞が電気スパイクを生成することから提案されたモデルであるため、一般に、指数関数的に減衰するシナプス電流波形や、膜電位が指数関数的に減少するリーク機構のような神経科学的特徴をもったニューロンモデルが主として用いられてきた。これに対して我々は、近年専用AIチップの分野で高い電力性能を示しているIn-memory computing(注2)の枠組みで回路実装できるように大胆にニューロンモデルを単純化して、多層SNNを構築した(図1)。

さらに、構築した多層SNNが効率的な動作をするよう、ニューロンの発火時刻を使って情報処理を実行する時間符号化に基ついた学習アルゴリズムを開発した。これにより各ニューロンが最大で一回しかスパイクを出力しないようにして、より高い電力効率が可能になった。

■ 効果

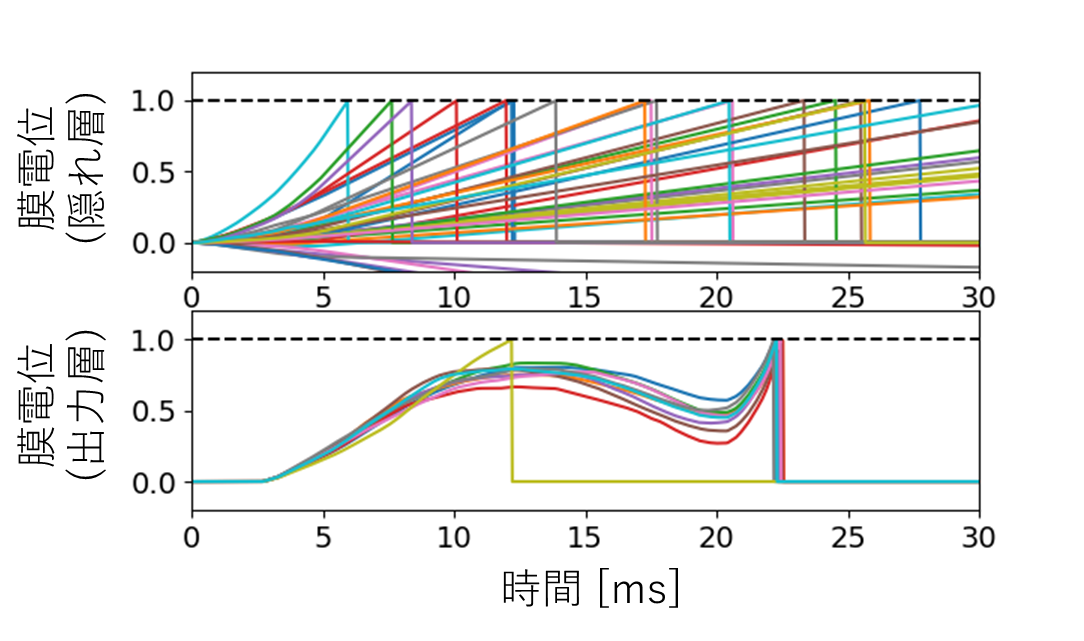

図2に標準的な画像認識タスクであるMNISTデータセットを学習したSNNの動作例を示している。これはコンピュータによるシミュレーション結果であるが、実際は、この動作をアナログ回路で行うことにより、低電力で認識タスクを実行することができる。本手法を、MNISTデータセットと、同様の画像認識タスクであるFashion-MNISTデータセットを用いて学習性能を検証した結果、既存の時間符号方式のSNNより高い性能を示すことが明らかになった。すなわち、専用AIチップでの回路実装に適したシンプルなニューロンモデルのSNNでも、より一般的な神経科学的特徴を備えたニューロンモデルのSNNと同等以上の学習性能があることを示唆している。

また、アナログ回路実装で問題となる製造ばらつきの影響も検討し、発火閾値や発火タイミングのばらつきなどに高い耐性を示すことも示された。さらに、In-memory computingの一般的な回路構成を簡略化した場合に相当するSNNモデルも構築し、その学習性能を評価することで、SNNを活用することの新たな可能性を示した。

本手法は、人工知能システムを構築する際に、集積回路実装まで踏み込んで協調設計することの重要さを示した先駆的な取り組みの一つといえる。SNNの学習アルゴリズムは近年急速に発展しており、さらに、アナログ集積回路設計も大きな進展を示している。この両者が適切に融合して設計できるようになると、より高性能の次世代ニューロモルフィック人工知能システムの構築が可能になると期待される。

5.発表雑誌:

雑誌名:「IEEE Transactions on Neural Networks and Learning Systems」(7月19日速報オンライン版)

論文タイトル:A Supervised Learning Algorithm for Multilayer Spiking Neural Networks Based on Temporal Coding Toward Energy-Efficient VLSI Processor Design

著者:Yusuke Sakemi, Kai Morino, Takashi Morie, Kazuyuki Aihara

DOI番号:10.1109/TNNLS.2021.3095068

6.問い合わせ先:

日本電気株式会社

酒見 悠介(さけみ ゆうすけ)

九州大学 大学院総合理工学研究院 非線形物性学研究室

准教授 森野 佳生(もりの かい)

九州工業大学 大学院生命体工学研究科

教授 森江 隆(もりえ たかし)

東京大学 特別教授・名誉教授

東京大学国際高等研究所ニューロインテリジェンス国際研究機構(WPI-IRCN)

副機構長・主任研究者 合原 一幸(あいはら かずゆき)

7.補足:

注1)スパイキングニューラルネットワーク (SNN)

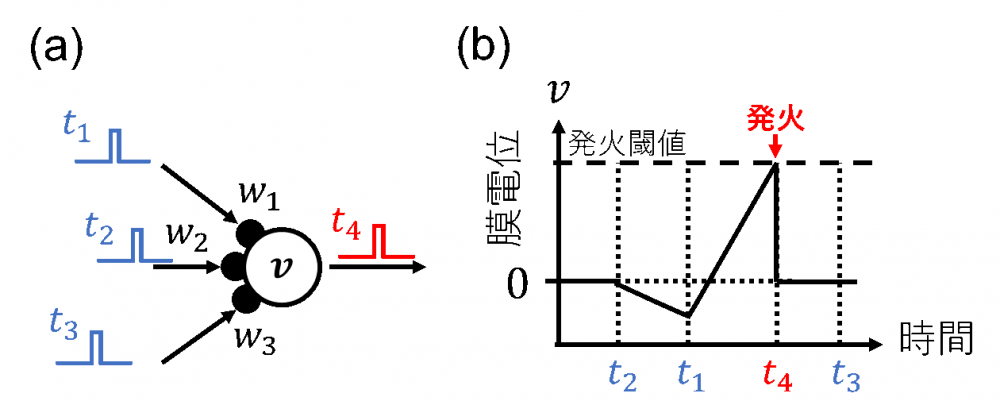

スパイキングニューロンを構成要素とするネットワーク。スパイキングニューロンは、スパイク(電気パルス)を受け取ることで、その重みに応じた電流が流れ、膜電位が変化していく。膜電位が発火閾値を超えるとスパイクを出力する。

注2)In-memory computing

既存のデジタルコンピュータのように、プロセッサとメモリを別チップで構成すると、両者の間の信号伝送に大きな電力を要することが知られており、演算量とメモリ量が莫大になる。AIチップでは特にその影響が顕著になる。そこで、低消費電力化を実現するために、計算の一部(積和演算)をメモリ上で行う「In-memory computing」が、AIチップ向け集積回路方式の一つとして採用されるようになった。この方式では、メモリの読み出し過程で電流を用いてアナログ的に積和演算を実行する。重みを抵抗で表現することで積和演算を電流総和で効率的に行うことができる。近年、ニューラルネットワークを超低消費電力で実装できることが示されてきている。

8.添付資料:

図1 ニューロンモデル。(a)ニューロンが時刻t1, t2, t3にスパイク入力を受け、時刻t_4にスパイクを出力している。(b)ある時刻までに入力を受けたスパイクの重みの合計値に従って、膜電位が一定の傾きで変化する。この特徴により回路実装が容易になる。

図2 MNISTを学習したSNN(784-800-10)の膜電位の時間発展の様子。上図は隠れ層の膜電位、下図は出力層の膜電位を表している。最も早く発火した出力層ニューロンのインデックスが予測値に対応する。