微細化と超低消費電力化へ前進

2018/12/03 科学技術振興機構,東京大学

ポイント

- 強誘電体のHfO2を使うと、消費電力が飛躍的に低いトランジスターとメモリーが作れると期待されているが、その動作原理と微細化の可能性は明らかでなかった。

- HfO2をゲート絶縁膜に用いたトランジスターが低電圧で動作する仕組みを実験的に解明。トンネル層に用いたメモリーは20nm径まで微細化可能なことを理論的に解明した。

- IoTデバイスの超低消費電力化に寄与し、より高度で充実したネットワーク・サービスの実現につながると期待される。

JST 戦略的創造研究推進事業において、東京大学 生産技術研究所の小林 正治 准教授らは、強誘電体注1)であるHfO2(二酸化ハフニウム)注2)をゲート絶縁膜注3)とするトランジスターがより低電圧で動作する仕組みを実験的に解明しました。さらに、HfO2をトンネル層とする強誘電体トンネル接合(FTJ)メモリー注4)が20nm径まで微細化可能なことを理論的に解明しました。

強誘電体HfO2をゲート絶縁膜として急峻なサブスレッショルド特性注5)を示す負性容量トランジスター(NCFET)注6)は超低電圧で動作するトランジスターとして注目を集めていますが、その動作原理は物理的に十分に解明されていませんでした。またFTJメモリーは大容量不揮発性メモリーとして注目されていますが、オン時とオフ時の抵抗比、読み出し動作時の電流などを考慮した微細化可能性は明らかではありませんでした。

本研究グループは、ゲート電流を高精度にその場測定しながらデバイス特性評価をすることで、強誘電体HfO2ゲート絶縁膜における自発分極の反転現象がサブスレッショルド特性の向上に大きく寄与することを、世界で初めて実験的に明らかにしました。また強誘電体分極を含めた自己整合ポテンシャル注7)と非平衡グリーン関数法注8)により、HfO2 FTJメモリーの電流の計算手法を構築し、材料物性と膜厚に対する依存性を系統的に調べることで、HfO2 FTJメモリーが20nm径程度まで微細化できることを理論的に示しました。

この成果は、超低電圧で動作するNCFETと、超低消費電力で大容量なFTJメモリーの設計指針に大きく貢献するものです。今後IoTにおける端末デバイスの超低消費電力化、それによる高度なIoTネットワークの展開、そしてビッグデータに基づく社会サービスの充実につながると期待されます。

本研究成果は、2018年12月4日および5日(米国太平洋標準時間)に「2018 IEEE International Electron Device Meeting」にて発表されます。

本成果は、以下の事業・研究領域・研究課題によって得られました。

戦略的創造研究推進事業 個人型研究(さきがけ)

研究領域:「素材・デバイス・システム融合による革新的ナノエレクトロニクスの創成」

(研究総括:桜井 貴康 東京大学 生産技術研究所 教授)

研究課題:「超低消費電力動作に向けたゲート絶縁膜の負性容量による急峻スロープトランジスタ技術の開発とナノワイヤ構造への応用」

研究者:小林 正治 東京大学 生産技術研究所 准教授

研究実施場所:東京大学 生産技術研究所

研究期間:平成27年10月~平成31年3月

JSTはこの領域で、材料・電子デバイス・システム最適化の研究を連携・融合することにより、情報処理エネルギー効率の劇的な向上や新機能の実現を可能にする研究開発を進め、真に実用化しイノベーションにつなげる道筋を示していくことを目指しています。上記研究課題では、超低電圧動作トランジスターとして強誘電性HfO2薄膜用いた負性容量トランジスター(NCFET)のデバイス設計・材料開発と、世界初の動作実証に取り組んでいます。

<研究の背景と経緯>

IoTでは、複数の端末を協調制御するセンサーネットワークが重要な役割を果たします。数年後には世界で年間1兆個ものセンサーがインターネットにつながると予想されていますが、それを実現するには、IoTデバイスをより低消費電力にすることが求められます。

デバイスの消費電力では、リーク電力(オフ状態でも消費される電力)が大きいことが問題となっています。これを低減するためには、抵抗オンオフ比の高いトランジスターと、メモリーの待機時の消費電力を抑える不揮発性メモリーが必要となります。

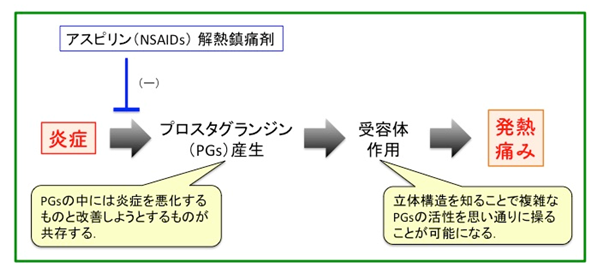

強誘電体をゲート絶縁膜とする負性容量トランジスター(NCFET)は、ゲート絶縁膜の容量が負になることでトランジスターの表面ポテンシャルが増幅されることを利用します。これにより、サブスレッショルド係数を通常のMOS(金属酸化物半導体)トランジスターの限界である60mV/decより小さくすることができるトランジスター技術として期待されています。

NCFETは2008年に提案されて以来さまざまなデバイスモデルや実験結果が報告されてきました。しかし、強誘電体の基本的性質である自発分極のダイナミクスと照らした、NCFETの動作原理の解明は十分にされていませんでした。

また、強誘電体トンネル接合(FTJ)メモリーは、微細化しやすく大容量化が期待される不揮発性メモリーです。FTJメモリーは2端子型の抵抗変化型メモリーであり、自発分極を反転させることで実効的なトンネル障壁を変調し、抵抗が高い状態と低い状態の切り替えを実現します。

FTJメモリーはこれまでもデバイスモデルや実験結果が報告されてきましたが、抵抗のオンオフ比、読み出し電流値、脱分極電界と保持特性をも考慮した微細化可能性については、十分に明らかになっていませんでした。

最近、CMOS(相補型MOS)プロセスと整合性の高い強誘電体HfO2が発見されてから、NCFETおよびFTJメモリーへの期待は大きくなってきており、次世代CMOSトランジスターおよびメモリー技術として研究開発を加速させるためにはデバイス物理の解明および微細化へ向けた指針が不可欠となります。

<研究の内容>

①強誘電体HfO2ゲート絶縁膜トランジスターにおける自発分極反転のサブスレッショルド特性に与える影響の実験的解明

本研究で小林准教授らは、強誘電体HfO2をゲート絶縁膜とするトランジスターにおいて、サブスレッショルド特性がより急峻になる仕組みを、強誘電体の性質で最も基本的な自発分極のダイナミクスとの対応という観点から実験的に解明しました。

強誘電体HfO2のキャパシタをMOSトランジスター上に集積した金属-強誘電体-金属-絶縁体-半導体型(MFMIS型)-FETは、図1に示すようにMFMキャパシタとMISFETを独立に設計・作りこむことができ、単一のデバイスでMFMIS-FETと比較のためのMISFETを評価することが可能でありデバイス物理の探求に適しています。しかし内部電極に電荷注入が起こると分極反転をサブスレッショルド領域で起こすことが難しくなります。そこで、MFMIS-FETに加えて、電荷が注入されたとしても分極反転をサブスレッショルド領域で起こるようにするために反強誘電体HfO2をゲート絶縁膜とした金属-反強誘電体-金属-絶縁体-半導体型(MAFMIS型)-FETを提案し作製しました。

まずMFMIS-FETのデバイス評価を行い、ゲート電圧の掃引の向きをゲート電流を測定しながら分極反転が起こるところで反転させることで20mV/dec程度の極めて急峻なサブスレッショルド特性を観測しました(図2)。これは急峻なサブスレッショルド特性が分極反転と電荷注入の相互作用によって起こることを示しています。

次にMAFMIS-FETのデバイス評価を行ったところ、分極反転が狙いどおりにサブスレッショルド領域で起こることを確認しました(図3)。特に顕著であるのは、分極反転電流が見かけ上2つに分裂して分極反転があたかも抑制されているように見えることです。これは分極反転が起こる際にサブスレッショルド領域に入ると、容量の小さい空乏層がゲート絶縁膜の下に形成され、ゲート絶縁膜側で脱分極場が生じ空乏層に大きな電圧降下が落ちてチャネル部の表面ポテンシャルが増幅されることを示しています。実際に、分極反転がサブスレッショルド領域で起こる場合には、起こらない場合に比べて確かにサブスレッショルド特性が向上していることが分かります。

以上の研究成果は、負性容量トランジスターにおける急峻なサブスレショルド特性の発現が分極反転のダイナミクスによるものとする動的なモデルを実験的に検証したものであり、次世代低消費電力トランジスターである負性容量トランジスターを研究開発するにあたって、より急峻なサブスレッショルド特性を持たせ、低電圧で動作させるためのデバイス設計に必要なデバイスモデルを構築する上で重要な成果といえます。

②自己整合ポテンシャルと非平衡グリーン関数法を用いたHfO2 FTJメモリーの微細化可能性の理論的提唱

本研究で東京大学 生産技術研究所の小林 正治 准教授らは、HfO2 FTJメモリーについて、自発分極を含めた自己整合ポテンシャルと非平衡グリーン関数による電流計算の計算手法を開発し、トレードオフ関係にある、抵抗オンオフ比、読み出し電流値、脱分極電界、を考慮して20nm径までの微細化可能性を理論的に示しました。

多層構造のFTJメモリーの電流計算を行うために、まず各バイアス電圧でのポテンシャル分布を強誘電体分極を含めて自己整合的に計算するモジュールを作成しました。このモジュールを非平衡グリーン関数で電流を計算するメインモジュールに組み込み、計算手法を構築しました。これまでに高抵抗オンオフ比を有する金属と半導体を電極とする強誘電体HfO2を用いた、金属-強誘電体-半導体型(MFS型)FTJメモリーの開発に成功しており、この実験データをもとにFTJメモリーの計算モデルのキャリブレーションを行いました。

MFS型FTJメモリーの設計パラメーターとして重要となるのが残留分極と半導体電極の基板濃度です。計算の結果、図4(a)に示すように残留分極値が下がると抵抗オンオフ比が下がることが分かりました。一般的に膜厚を薄くすると残留分極値が下がります。しかし図4(b)に示すように半導体電極の不純物濃度を下げることで抵抗オンオフ比が向上することから、薄膜化に伴う残留分極低減による抵抗オンオフ比の減少を補償することができることが分かりました。

一般的に脱分極電界は強誘電体の膜厚を薄くするほど大きくなる傾向があります。脱分極電界が強誘電体の保持電界を超えるとメモリーとしての保持特性が得られないために脱分極電界は低く抑える必要があります。計算上では図4(c)に示すように、薄膜化するにつれて残留分極が低減することを考慮すると脱分極電界は保持電界を超えないことが分かりました。

次にターゲットとする読み出し電流に対して要求される強誘電体HfO2膜厚と得られる抵抗オンオフ比を計算したのが図5です。読み出し電流100nAをターゲットとしても強誘電体HfO2を1~1.5nmまで薄膜化することができれば、抵抗オンオフ比200%以上を維持したままメモリーセル直径を20nm程度まで微細化可能であることが明らかとなりました。

以上の研究成果は、今後のFTJメモリーの研究開発における有用な計算手法と重要な設計指針を示すものであるといえます。そして他の不揮発性メモリーと比べてもHfO2 FTJメモリーが微細化とそれによる大容量化という点で十分に競争力を持つことを示す重要な成果といえます。

<今後の展開>

強誘電体HfO2ゲート絶縁膜トランジスターに関しては、分極反転によるサブスレッショルド特性改善のモデルを、より集積化に向いている金属-強誘電体-半導体型(MFS型)トランジスターを用いて引き続き検証します。本トランジスターをロジックトランジスターとして実用化するためには、印加電圧の掃引方向によって素子特性が変わるヒステリシスを引き起こさない方策が必要です。ヒステリシスがなく急峻なサブスレッショルド特性を持つ強誘電体HfO2ゲート絶縁膜トランジスターを設計することで次世代のCMOSトランジスター技術としての研究開発が加速されることが期待されます。

強誘電体HfO2 FTJメモリーに関しては、ランダムアクセスメモリーとして動作させるために本研究での微細化の指針に加えてセレクタが必要になります。強誘電体HfO2と界面層および電極材料をエンジニアリングすることでFTJメモリー自身にセレクタを内蔵するデバイス設計を目指します。セレクタが内蔵されたFTJメモリーは大容量ストレージメモリーあるいは人工知能ハードウェア応用に向けて研究開発が加速されることが期待されます。

<参考図>

![]()

図1 作製したMFMIS-FETの外観(左)および断面図(右)

断面図は上がゲート方向、下がチャネル方向を示します。この構造ではMFMキャパシタとMISFETを独立に設計し、MFMIS-FETとMISFETを単一のデバイスで評価できます。

![]()

図2 ジルコニウム30%ドープのHfO2をゲート絶縁膜とするMFMIS-FETのドレイン電流対ゲート電圧特性

ゲート電圧掃引の向きを分極反転時に切り替えることで30mV/dec程度の急峻なサブスレッショルド特性を観測しました。

![]()

図3 MAFMIS-FETのドレイン電流およびゲート電流対ゲート電圧

全てジルコニウム90%ドープですが、上部電極と内部電極の面積比が(左)1:8、(中)1:14、(右)1:32。例えば(中)の順方向掃引では分極反転がサブスレッショルド領域で起こりませんが、逆方向掃引では分極反転がサブスレッショルド領域で起こりサブスレッショルド特性が順方向に比べてより急峻になっていることが分かります。

![]()

図4 HfO2 FTJメモリーのオン電流、オフ電流、抵抗オンオフ比に関する

(a)残留分極依存性

(b)半導体電極不純物濃度依存性

(c)脱分極場の界面層膜厚および強誘電体膜厚依存性

残留分極が下がると抵抗オンオフ比が下がりますが、不純物濃度を下げることで抵抗オンオフ比を上げることができることが分かります。

![]()

図5 HfO2 FTJメモリーについて、ターゲットとする読み出し電流値に対して、 抵抗オンオフ比および必要な強誘電体膜厚とメモリーセル直径の関係を計算したもの

(a)10nAターゲット

(b)100nAターゲット

100nAの読み出し電流値をターゲットとしても1.0~1.5nm程度まで強誘電体を薄膜化することで20nm径まで微細化できます。

<用語解説>

- 注1)強誘電体

- 結晶格子が中心非対称性を有し、電界によって結晶格子中の原子が変位することで双安定状態を有し、電界がない状態でも自発的な分極を保持する誘電体材料の一種。

- 注2)HfO2(二酸化ハフニウム)

- HfO2は二酸化ケイ素(SiO2)よりも誘電率が高く、アモルファス相の常誘電体は現在の先端CMOSトランジスターのゲート絶縁膜として用いられています。近年、HfO2の特定の結晶層で強誘電性が発見されました。HfO2はすでにCMOSプロセスで用いられていることから、強誘電体HfO2は集積化デバイスに適した新機能材料として期待されています。

- 注3)ゲート絶縁膜

- 現在、大規模集積回路を構成しているトランジスターは金属(Metal)、酸化物(Oxide)、半導体(Semiconductor)からなるMOS構造をとっています。金属が入力電圧を印加するゲート電極であり、半導体に流れる電流を制御します。金属と半導体の間には絶縁膜が必要であり、この絶縁膜のことをゲート絶縁膜と呼びます。通常は常誘電体のシリコンまたは金属の酸化物が用いられます。

- 注4)強誘電体トンネル接合(FTJ)メモリー

- 強誘電体ナノ薄膜を上部・下部の電極で挟んだ2端子構造のデバイス。電圧によって強誘電体の自発分極の向きを反転させることでトンネル障壁高さが変調され、低抵抗なオン状態と高抵抗なオフ状態を切り替えることができ、不揮発性メモリーとして動作します。FTJは強誘電体トンネル接合(Ferroelectric Tunnel Junction)の略。

- 注5)サブスレッショルド特性

- 通常の電界効果トランジスターにおいては、閾値(スレッショルド:Threshold)電圧より低いゲート電圧領域をサブスレッショルド領域と呼び、電流は拡散伝導に支配されゲート電圧の変化に対して通常指数関数的に変化します。この領域で電流が一桁増大するために必要なゲート電圧の増加量をサブスレッショルド係数とよび、通常mV/decという単位で表します。

- 注6)負性容量トランジスター(NCFET)

- 通常のMOS(金属酸化物半導体)トランジスターのゲート絶縁膜を強誘電体薄膜で置き換えたもので、強誘電体で生じる負性容量を利用して表面ポテンシャルを増大させ、サブスレッショルド特性を急峻にできるとされるトランジスター。

FETは電界効果トランジスター(Field Effect Transistor)の略で、ゲート電極に電圧をかけて生じる電界によって電流を制御するトランジスターのこと。負の誘電率を持つ物質は、物質にかかる電圧と分極電荷の符号が通常の誘電体とは逆の関係にある物質です。物質にかかる電圧に対して生じた電荷の比を負性容量(Negative Capacitance:NC)と呼びます。近年、強誘電体HfO2が負の誘電率を持つことが発見され、NCFETの材料として期待されています。 - 注7)自己整合ポテンシャル

- 強誘電体トンネル接合(FTJ)において、ポテンシャル分布とその内部の電荷状態が、与えられた境界条件(全体のポテンシャル分布の和は印加電圧に等しい、電荷中性条件が成り立たなければならない、など)のもと、互いにつじつまが合うように計算する手法。

- 注8)非平衡グリーン関数法

- ナノ構造を持つデバイスの電流特性を量子力学に基づいて計算する手法。電流を計算するためには2端子間の電子の波動関数の透過率が必要であり、この透過率は一般的に系のハミルトニアンをもとに計算されるグリーン関数を用いて表されます。デバイスに電圧が印加された非平衡な状態でグリーン関数を計算し、最終的に2端子間の電流を求めます。

<論文情報>

タイトル:“Experimental Study on the Role of Polarization Switching in Subthreshold Characteristics of HfO2-based Ferroelectric and Anti-ferroelectric FET”

(強誘電体および反強誘電体HfO2をゲート絶縁膜とするトランジスタにおけるサブスレショルド特性に対する分極反転の影響に関する実験的検討)

タイトル:“Scalability Study on Ferroelectric-HfO2 Tunnel Junction Memory Based on Non-equilibrium Green Function Method with Self-consistent Potential”

(自己整合ポテンシャルと非平衡グリーン関数に基づく強誘電体HfO2トンネル接合メモリーの微細化可能性に関する研究)

<お問い合わせ先>

<研究に関すること>

小林 正治(コバヤシ マサハル)

東京大学 生産技術研究所 准教授

<JST事業に関すること>

中村 幹(ナカムラ ツヨシ)

科学技術振興機構 戦略研究推進部

<報道担当>

科学技術振興機構 広報課

東京大学 生産技術研究所 広報室