2021-05-30 産業技術総合研究所

ポイント

- SiC縦型MOSFETとSiC CMOSをワンチップに集積し、スイッチング動作を実証

- 独自のデバイス構造を開発したことでSiC CMOSの出力電流増大と高電圧からの絶縁を両立

- 小型軽量化・高性能化・高機能化によって電力変換機器の適用先拡大に期待

概要

国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)先進パワーエレクトロニクス研究センター【研究センター長 山口 浩】パワーデバイスチーム 岡本 光央 主任研究員、原田 信介 研究チーム長、パワー回路集積チーム 八尾 惇 研究員、佐藤 弘 研究チーム長は、炭化ケイ素(SiC)半導体を用い、耐電圧1.2 kVクラスの縦型MOSFETと、CMOS構成された駆動回路を同一チップに集積したモノリシックパワーICを世界で初めて実現し、そのスイッチング動作を確認した。

SiCモノリシックパワーICは、電力変換機器の小型軽量化や損失低減などに貢献できるが、SiC CMOSの出力大電流化と高電圧からの絶縁の両立という困難な課題があり、これまで実現には至っていなかった。今回、産総研独自のデバイス構造を新たに開発し、SiC CMOSの高電圧絶縁に加えて出力電流増大を同時に達成することに成功した。この技術に基づいて、CMOS駆動回路をSiC縦型MOSFETと同一チップ上に集積したSiCモノリシックパワーICを作製し、スイッチング動作を世界で初めて実証した。今回開発した技術は、SiCセンサーやSiCロジック回路などの機能集積に道を拓く成果であり、電力変換機器用途の拡大が期待できる。

なお、この技術の詳細は、2021年5月30~6月3日にオンラインで開催されるThe 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)で発表される。

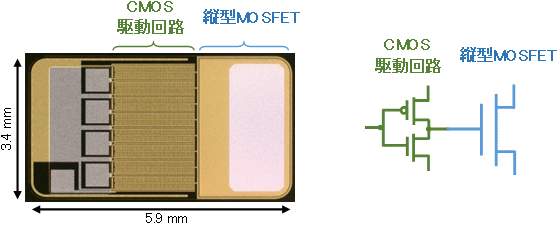

開発したSiCモノリシックパワーICの顕微鏡写真とその等価回路

開発の社会的背景

近年、地球温暖化問題は深刻さを増しており、社会全体の省エネルギー化(CO2削減)が急務となっている。電力エネルギーの変換・制御を行うパワーエレクトロニクス(パワエレ)技術は、家電製品や産業用機器などの省エネルギー化を可能とするキーテクノロジーの一つである。2050年のカーボンニュートラルの実現に向けて、パワエレ技術を適用した電力変換機器を様々な場所に大量導入する必要がある。電力変換機器の小型軽量化、高性能化、高機能化は、電力変換機器の適用先を拡大し、大量導入するうえで重要であり、その中核を担うパワーデバイスの革新が不可欠である。

SiCはパワーデバイス材料として従来用いられてきたSiに比べて優れた物性を持ち、大電流・高電圧をより低損失で扱えるSiC縦型MOSFETが既に実用化に至っている。一方、SiCモノリシックパワーICについては、製造の難しさからほとんど報告がされてこなかった。特に、簡素な回路構成が可能で、かつ低消費電力なCMOS駆動回路を搭載したSiCモノリシックパワーICは、これまで実現されていなかった。その最大の理由は、高電圧でも壊れないように設計されたSiC CMOS駆動回路は出力電流が小さく、SiC縦型MOSFETをスイッチング動作させることが困難であったためである。

研究の経緯

産総研は、SiCパワーデバイスの量産に向けた技術開発を進めてきた。これまで独自構造のSiCパワーMOSFET(トランジスタ)として、第1世代のIE-MOSFET、第2世代のIE-UMOSFETを開発した。また、駆動回路として使用されるSiC CMOSに関する研究として製造プロセスの要素技術開発や特性評価も行ってきた。さらに、SiCパワーデバイスを用いたスイッチング技術についても研究開発を行ってきた。今回、これらの研究成果を結集し、同一チップ上にIE-UMOSFETとSiC CMOSを集積したSiCモノリシックパワーICを開発し、スイッチング動作を実証した。

なお、本研究開発は、国立研究開発法人 新エネルギー・産業技術総合開発機構の委託事業「NEDO先導研究プログラム/エネルギー・環境新技術先導研究プログラム(2020~2021年度)」による支援を受けた。

研究の内容

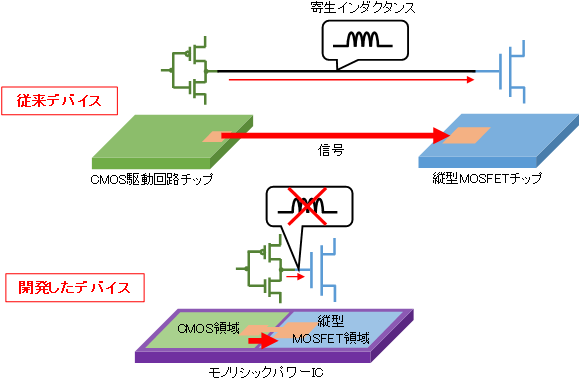

今回、産総研は、縦型MOSFETとCMOS駆動回路を同一チップに集積したSiCモノリシックパワーICを開発した。その概念図を図1に示す。従来は、CMOS駆動回路と縦型MOSFETは別々のチップに分かれており、その信号配線は金属ワイヤやプリント基板などを介して行われている。縦型MOSFETには高電圧が印加されるため、CMOS駆動回路とは十分な絶縁距離が必要であり、これが電力変換機器の小型軽量化を阻む要因となる。また、信号配線に存在する寄生インダクタンス(意図しない誘導成分)により、スイッチング動作が悪影響を受け、損失が増大する原因となる。開発したモノリシックパワーICは縦型MOSFETとCMOS駆動回路を同一チップに集積化することで、信号配線長を最小化できるため、小型軽量化と寄生インダクタンス低減が可能となった。

図1 開発したモノリシックパワーIC技術の概念図

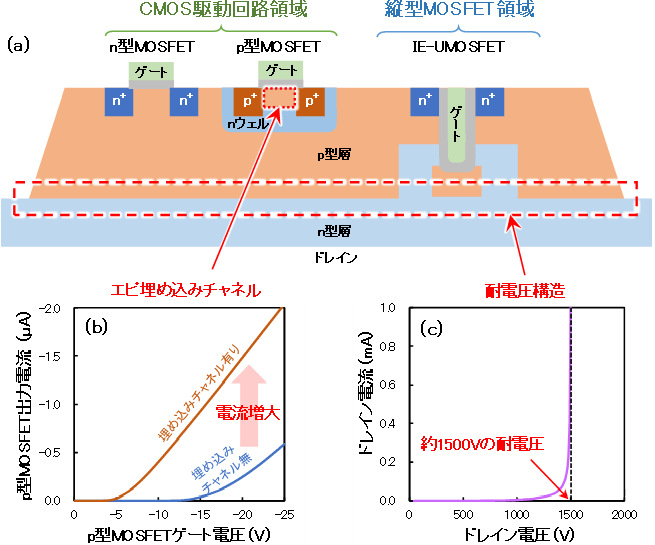

開発したSiCモノリシックパワーICの特徴を図2に示す。図2(a)に示すとおり、SiCモノリシックパワーICは縦型MOSFET領域とCMOS駆動回路領域の二つの領域から構成される。縦型MOSFETには、産総研が開発したIE-UMOSFETを採用した。CMOS駆動回路は、IE-UMOSFETと共通のp型層上に形成し、(1) p型MOSFET出力電流増大および (2) 耐電圧、の2点を両立させることに成功した。以下に2点の具体的内容を記述する。

(1) p型MOSFET出力電流増大:一般的にSiC CMOSは、p型MOSFET出力電流がn型MOSFET出力電流よりも大きく劣ることが問題であり、SiC CMOS駆動回路によるスイッチング動作実現の障害となっていた。我々はIE-UMOSFETのp型層が高結晶品質なエピタキシャル膜で形成されているという特徴を活用し、ほとんど製造プロセスを変更することなくエピ埋め込みチャネルを形成した。これにより、p型MOSFET出力電流を4倍に増大させることに成功した(図2(b))。

(2) 耐電圧:IE-UMOSFETと共通の耐電圧構造内にSiC CMOSを形成することにより、新たな製造プロセスを追加することなく、CMOS駆動回路を1500 Vのドレイン電圧から絶縁することに成功した(図2(c))。

図2 今回開発したSiCモノリシックパワーICの (a) 断面模式図、(b) エピ埋め込みチャネルの効果、(c) 耐電圧特性

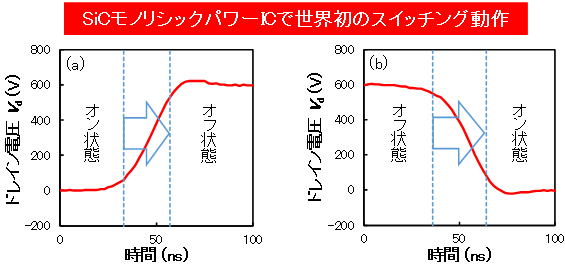

作製したSiCモノリシックパワーICのスイッチング動作波形を図3に示す。ドレイン電圧600 V、ドレイン電流10 Aでスイッチング動作させた。オン状態からオフ状態へのスイッチング動作(ターンオフ)、およびオフ状態からオン状態へのスイッチング動作(ターンオン)の両波形が得られ、SiCモノリシックパワーICによるスイッチング動作を世界で初めて実証した。

図3 SiCモノリシックパワーICのスイッチング動作波形

(a) ターンオフ波形、(b) ターンオン波形

今後の予定

今後、SiC CMOS駆動回路の出力電流をさらに増大させ、SiCモノリシックパワーICの高速スイッチングを目指す。加えて、センサーやロジック回路等も集積し、高機能化を進めることによって利便性を高め、電力変換機器の適用先拡大に貢献する。

用語の説明

- ◆炭化ケイ素(SiC)半導体

- 炭素(C)とケイ素(Si)からなる化合物半導体。従来のSi半導体と比べパワーデバイスの特性向上につながる物性値が優れている。SiCをパワーデバイスに用いると、Siのデバイスより1桁高い耐電圧が得られるため、次世代のパワーデバイス用材料として期待されている。

- ◆縦型MOSFET

- MOSFETとは、金属/酸化膜/半導体電界効果トランジスタ(Metal/Oxide/Semiconductor Field Effect Transistor)のこと。制御電極(ゲート)の電圧によって内部の導通状態を変え、トランジスタの入力電極(ソース)と出力電極(ドレイン)の間のスイッチング状態(内部の回路のオンオフの状態)を制御する。使用される半導体の伝導型によって、正の制御電圧で動作するn型MOSFETと負の制御電圧で動作するp型MOSFETの2種類がある。SiCパワーデバイスでは、n型MOSFETを使用し、ソースとゲート電極が基板の表側、ドレイン電極が基板の裏側に配置される縦形構造が一般的である。

- ◆CMOS

- 相補型(Complementary)MOS。p型MOSFETとn型MOSFETを組み合わせた電子回路。片方がオン状態の時、他方がオフ状態となる相補的な動作をする。低消費電力、回路構成が簡素になる、など多くの利点がある。なお、すべての電極が基板の表側に配置される横型構造である。

- ◆駆動回路

- MOSFETの制御電極(ゲート)へ送る信号を作るための電子回路。

- ◆モノリシックパワーIC

- メインデバイスであるパワーデバイスと、駆動回路等の周辺回路を同一チップ上に集積した集積回路(IC)。

- ◆電力変換機器

- 半導体トランジスタで形成されたパワーデバイスのスイッチング(内部回路のオンオフ)を利用して、電力の変換(直流・交流変換や電圧変換)や制御を担う機器。

- ◆IE-MOSFET

- Implantation and Epitaxial MOSFETと呼ばれる産総研で開発したSiC縦型MOSFET。制御電極(ゲート)でスイッチング状態が制御される半導体領域(チャネル)を、表面へ平面的に形成したプレーナー型構造をもつ。チャネルを高品質結晶領域に形成することにより、オン状態での抵抗を低減した。

- ◆IE-UMOSFET

- Implantation & Epitaxial Trench MOSFETと呼ばれる産総研で開発したSiC縦型MOSFET。制御電極(ゲート)でスイッチング状態が制御される半導体領域(チャネル)を、表面に設けた溝(トレンチ)の側壁に形成したトレンチ型構造をもつ。IE-MOSFETにトレンチ型を応用した構造であり、オン状態での抵抗を大幅に低減した。

- ◆エピタキシャル膜

- 下地の結晶構造を引き継ぐように結晶成長(エピタキシャル成長)させた薄膜。高い結晶性を有し、結晶欠陥が少ない。成長の際に不純物を導入することにより、n型、p型の伝導型制御が可能。

- ◆エピ埋め込みチャネル

- MOSFETの制御電極(ゲート)でスイッチング状態が制御される半導体領域をチャネルと呼ぶが、チャネル領域の不純物濃度を変化させたものを埋め込みチャネルという。オフ状態からオン状態への遷移が始まる制御電圧(閾値ゲート電圧)とオン状態での電流の流れやすさ(チャネル移動度)を改善するために導入される。この埋め込みチャネルを、エピタキシャル膜で形成したものをエピ埋め込みチャネルと呼ぶ。エピタキシャル膜の高い結晶性により改善効果が高いが、通常は追加のエピタキシャル成長が必要となり製造プロセスへの負荷が大きい。