2022-07-22 東芝デバイス&ストレージ株式会社

東芝デバイス&ストレージ株式会社は、低オン抵抗でスイッチング損失を大幅に削減したSiC(炭化ケイ素) MOSFET注1を開発しました。本技術により、当社の第二世代SiC MOSFET製品と比較して電力のオンとオフが切り替わるスイッチング時の電力損失(以下、スイッチング損失)を約20%削減できることを確認しました。

電力を供給、制御する役目を果たすパワー半導体は、あらゆる電気機器の省エネルギー化やカーボンニュートラルの実現に不可欠な半導体であり、自動車の電動化や産業機器の小型化などを背景に、今後も継続的な需要拡大が見込まれています。SiCは、従来のSi(シリコン)よりも高耐圧、低損失化が可能な次世代のパワー半導体材料として注目されていますが、信頼性の向上が課題となっています。当社は、第二世代の製品のSiC MOSFET内部に、PNダイオードと並列にショットキーバリアダイオード(SBD)を配置する構造を採用することでこの課題を解決しました。しかしSBDを内蔵することでMOSFETとして動作する領域が減少するため、単位面積あたりのオン抵抗RonAの増加や、オン抵抗と高速性を示した性能指数Ron*Qgdが大きくなることで損失が増加します。またRonAが高いことにより所望のオン抵抗Ronを得るためにはチップ面積を大きくする必要があり、コストが高くなるというさらなる課題がありました。

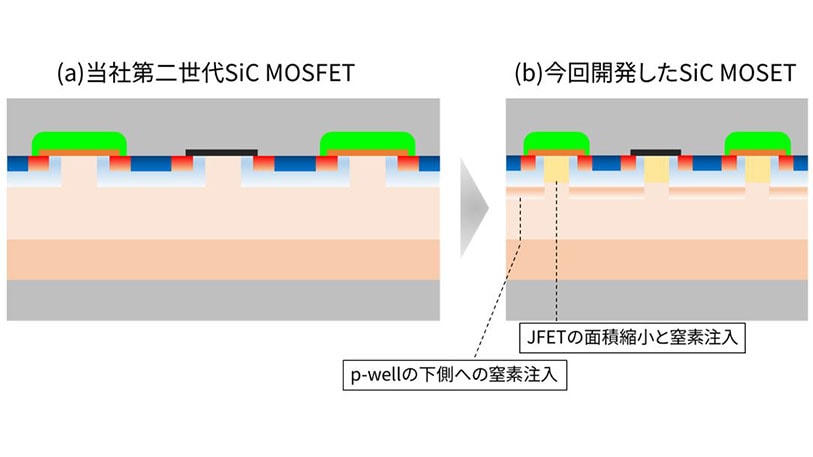

そこで当社は、SBDを内蔵した上でRonAを削減するデバイス構造を開発しました。SiC MOSFETのp型の広い拡散領域(p-well)の下側に窒素を注入することにより、広がり抵抗Rspread注2を削減し、SBDの電流を増加させました。また、JFET注3領域にも窒素を注入することで、JFETの面積を小さくすることによりRonAを上げることなく帰還容量を小さくしました。このデバイス構造を適用することで、当社第二世代の製品と比較してRonAを43%削減注4し、Ron*Qgdを80%削減注5し、スイッチング損失を約20%削減注6できることを、実際にデバイスを試作し確認しました。さらに、今回SBDを配置することでRonAの変動が起きず安定した動作が得られることも確認しました。

当社は、本技術の詳細を、ドイツ・ニュルンベルク、およびオンラインで開催されたパワー半導体の国際学会「PCIM Europe 2022」で5月12日に発表しました。本技術を適用した第三世代のSiC MOSFETを2022年8月下旬から量産する予定です。

注1 MOSFET:Metal Oxide Semiconductor Field Effect Transistor(金属酸化膜半導体電界効果トランジスター)の略で、トランジスターの構造の一種。

注2 p-well下部の拡散抵抗のこと。

注3 JFET:Junction Field Effect Transistor(接合型電界効果トランジスター)の略で、電圧制御のトランジスターのこと。

注4 当社第二世代SiC MOSFETのRonAを1とした場合の、今回開発した1.2kVのSiC MOSFETの比較。当社調べ。

注5 当社第二世代SiC MOSFETのRon*Qgdを1とした場合の、今回開発した1.2kVのSiC MOSFETの比較。当社調べ。

注6 当社第二世代Si CMOSFETと今回開発した1.2kVのSiC MOSFETの比較。当社調べ。

今回開発したデバイス構造

![]()

RonAとRon*Qgdの削減結果(当社調べ)

![]()

(a)当社第二世代SiC MOSFETのRonAを1とした場合の、今回開発した1.2kVのSiC MOSFETと他社のSiC MOSFETとのRonAの比較

![]()

(b)当社第二世代SiC MOSFETのRon*Qgdを1とした場合の、今回開発した1.2kVのSiC MOSFETと他社のSiC MOSFETとのRon*Qgdの比較