従来比18倍のパケット処理性能を実現し、アプリケーションのサーバー集約率を向上

2020-11-27 株式会社富士通研究所

株式会社富士通研究所(注1)(以下、富士通研究所)は、仮想環境におけるネットワーク処理の主要機能である仮想ルーターを高速化する技術を開発しました。

汎用サーバー上の仮想環境でネットワーク処理のインフラ機能と複数のアプリケーションを集約するサーバー仮想化は、データセンタだけでなく Mobile Edge Computing(注2)(以下、MEC)や基地局といったエッジ領域にまで拡がりつつあり、交通管制などの社会インフラやスポーツ観戦などのエンターテインメントで活用されています。しかし、使用するデータ量の増加とシステムの複雑化に伴って、仮想ネットワークのパケット処理に要するCPUリソースが増加します。そのため、1台のサーバー上で稼働できるアプリケーション数が減り、サーバー集約率の低下につながっています。

今回、これらの課題を解決するため、仮想ネットワークのルーター機能をFPGA(注3)にオフロードして処理するとともに、性能ボトルネックであったパケット宛先制御を高速化する技術を開発しました。これにより、従来の仮想ルーターと比較して、パケット処理性能を約18倍高速化し、CPUリソースを約13分の1に削減しました。

本技術により、低負荷・高性能な仮想ネットワークを提供し、5G時代の大量データを活用したビジネスにおいて、サーバーの利用効率を向上させ、企業のDXを支えます。

開発の背景と課題

企業のデジタル革新が進む中、汎用サーバー上の仮想環境を用いて、複数のアプリケーションとネットワーク処理機能を集約するサーバー仮想化が広く一般化してきています。また様々な企業におけるDXの加速により、アプリケーション同士が連携して動作する新たなサービスも生まれています。このような背景から、アプリケーションが取り扱うデータ量は増加傾向にあり、ネットワークの複雑化と負荷増加が問題となっています。

その中で、効率的なサーバー仮想化を実現するためには、柔軟なネットワーク構成に必要な仮想ルーターのパケット処理性能の向上と、ネットワーク処理に用いられるCPUリソースの削減が課題となっています。これらの課題を解決することにより、サーバー上で動作するアプリケーション数の増加、または必要なサーバー台数の削減を実現することができ、お客様の投資コストを低減します。

開発した技術

今回、仮想ルーター機能をFPGAにオフロードし処理することでCPUの処理を肩代わりするとともに、パケットの宛先制御を高速化する技術を開発しました。これにより、ネットワーク性能を高速化するとともに、ネットワーク処理で使用するCPUリソースを大幅に削減します。

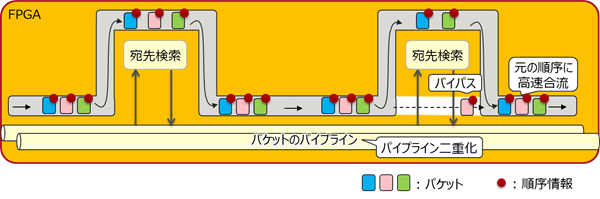

- 高速パケット宛先検索技術従来は、パケット順を変更することなく全パケットで同じ処理を実施することで高速処理を行っていました。仮想ルーター処理の入出力でパケット順が変わると、アプリケーションでは再送が発生し、品質低下やシステムの負荷増加につながります。本技術では、パケットのパイプライン上でパケットと別に順序情報を保持し、多段にわたる宛先検索処理において前段検索の結果から不要となった次段検索をバイパスさせて合流させる際に、パケットのパイプラインの順序情報をもとに高速にパケットを元の順序に戻します。高速なパイプライン処理を維持しつつメモリアクセスを低減させるとともに、パイプライン処理を二重化することで、パケット処理性能を向上させます。

図1:高速パケット宛先検索技術 - 検索テーブルのハイブリッドメモリ管理技術宛先検索処理ではメモリ内にある複数のテーブルを検索して宛先を決定しますが、高速で小容量なFPGAの内部メモリと大容量の外部メモリとを、宛先検索処理を止めずに自動的に切り替える機能を開発しました。接続数の増加に伴って検索テーブル群のメモリ使用量が増加して内部メモリの空き容量が少なくなった場合に、容量あたりのアクセス頻度が低い検索テーブルをバックグラウンドで外部メモリに同期しておき、検索処理を止めることなく外部メモリの検索テーブルに自動で切り替えます。これにより、大規模システムにおいて通信先が多く、大きな検索テーブルが必要な場合でも、外部メモリへのアクセスを抑えて、安定したパケット処理性能を実現します。

図2:ハイブリッドメモリ管理技術

効果

本技術を用いて、オープンソースの代表的な仮想ルーターである「Tungsten FabricTM」を、高速メモリHBM2(注4)を搭載した「インテル® Stratix® 10 MX FPGA」上に実装させ、汎用サーバー上でのオフロード効果の検証を行いました。100Gbpsのイーサネットで接続したサーバー2台に仮想マシンを4台ずつ動かし、各仮想マシン間で通信を行って仮想ルーターの性能を測定したところ、従来手法では13.8Mppsだったパケット処理性能に対して、250Mppsと約18倍の高速化を実現しました。また、使用CPUコア数も従来の13コアから1コアに削減しました。

本技術を用いることでアプリケーションのサーバー集約率を向上させることが可能となります。例えばスタジアムにおける映像配信サービスがより少ないサーバー台数での運用が可能となるなど、キャリア事業者向けの基地局やMECをはじめとした5G時代の大量データを活用したインフラビジネス領域におけるサーバーの利用効率を向上させ、お客様のDXを基盤から支えます。

今後

当社は、本技術のさらなる性能向上と機能拡充を行うとともに、お客様のDXユースケースを想定した検証を進め、2021年度中の実用化を目指します。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

Intel、インテル、Intel ロゴ、Stratix は、Intel Corporation またはその子会社の商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 本社 神奈川県川崎市、代表取締役社長 原 裕貴。

- 注2 MEC:

- 主に移動通信網において、基地局などに配備したサーバーやストレージにデータ処理を行わせることで、コアネットワークの遅延低減や負荷分散を実現する技術。

- 注3 FPGA:

- Field Programmable Gate Arrayの略。論理回路を書き換え可能な大規模半導体デバイス。

- 注4 HBM2:

- FPGAと同一パッケージに内蔵された高速大容量なデータ転送が可能なメモリ。

本件に関するお問い合わせ

株式会社富士通研究所

プラットフォーム革新PJ