2023-03-23 新エネルギー・産業技術総合開発機構

NEDOは「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」に取り組んでおり、今般、東京大学生産技術研究所を中心とする研究グループと共同で、1チップでパワー半導体のエネルギー損失を低減する「自動波形変化ゲート駆動ICチップ」を世界で初めて開発しました。

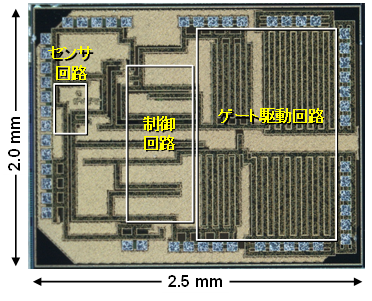

本ICチップ上には、出力電流を切り替えるゲート駆動回路、電流切り替えタイミングを決定するセンサー回路、電流波形を変化させる制御回路の三つを搭載しています。これにより、パワー半導体のゲート端子を駆動する電流波形を自動で最適なタイミングに制御し、エネルギー損失を低減する回路を実現しました。また、本ICチップとパワー半導体を組み合わせた実証試験により、600V、80Aの条件下でエネルギー損失を約49%低減できることを確認しました。

今後はさらなる改良を進め、2050年カーボンニュートラルへの道筋を示し、パワーエレクトロニクス機器の省エネ化による温室効果ガスの排出量削減に貢献します。

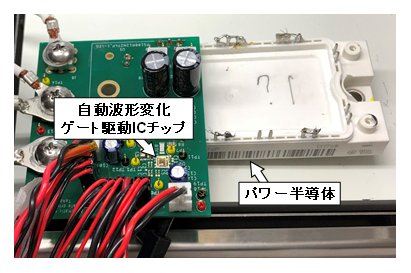

図1 開発した「自動波形変化ゲート駆動ICチップ」の写真 (提供:東京大学生産技術研究所)

1.概要

インバーターなど電力の変換や制御を行うパワーエレクトロニクス機器の分野では、さらなる省エネ化の要求に応えるため、さまざまなパワー半導体のエネルギー低損失化に関する研究開発が行われてきました。

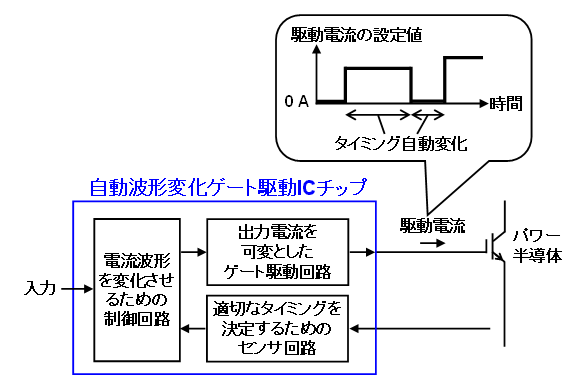

一般にパワー半導体の課題である高電圧、大電流環境での出力電流のスイッチオン、スイッチオフの切り替え(スイッチング)時に発生するエネルギー損失の低減と、パワー半導体が壊れる原因となるノイズ※1の低減はトレードオフの関係にあります。この問題を解決する手法として「出力電流を可変としたゲート駆動回路」、「適切なタイミングを決定するためのセンサー回路」、「電流波形を変化させるための制御回路」を搭載した「自動波形変化ゲート駆動回路」でパワー半導体を制御する手段※2がありますが、回路装置のサイズが14cm×7cmと大型のため、この方法では実製品への搭載までは到達できませんでした。

このような背景のもと、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)は、2021年度から進める「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業※3」(以下、本事業)において国立大学法人東京大学生産技術研究所を中心とする研究グループ(以下、本研究グループ)と共同で、大口径インテリジェント・シリコンパワー半導体の開発に取り組んでいます。パワー半導体のエネルギー低損失化に関する研究開発の多くはパワー半導体そのものの開発でエネルギー損失の低減を目指すのに対し、本研究グループでは、パワー半導体の「ゲート端子を最適に駆動する」という「使いこなし」でエネルギー損失の低減ができることに着目し、「出力電流を可変としたゲート駆動回路」、「適切なタイミングを決定するセンサー回路」、「電流波形を変化させる制御回路」の三つの回路を1チップ上に搭載した「自動波形変化ゲート駆動ICチップ」の開発を進めてきました。

そして今般、世界初となるパワー半導体のゲート端子を自動で最適に駆動制御する「自動波形変化ゲート駆動ICチップ」の開発に成功しました。さらに、本ICチップとシリコンのパワー半導体を組み合わせた実証試験により、600V、80Aの条件でエネルギー損失を約49%低減できることを確認※4しました。

2.今回の成果

(1)「自動波形変化ゲート駆動ICチップ」の開発

今回開発した「自動波形変化ゲート駆動ICチップ」では、駆動回路・センサー回路・制御回路の三つの回路を小型化し、図1に示すように、1つのICチップ上(サイズ:2.5mmX2.0mm)で実現することに成功しました。回路サイズが従来の2万分の1程度になるため、一般のパワーエレクトロニクス機器などの製品にも実装して、パワー半導体のエネルギー損失を低減できます。

本ICチップの特徴は、従来の汎用的なゲート駆動ICの代わりに本ICチップをパワー半導体のゲート端子に接続することで、誰でも容易に使えることです。また、本技術は実証に使用したシリコンパワー半導体に限らず、炭化ケイ素(SiC)などさまざまなパワー半導体のゲート駆動に適用可能です。

図2 開発した「自動波形変化ゲート駆動ICチップ」の回路イメージ (提供:東京大学生産技術研究所)

(2)実証内容

今回開発したICチップでゲート制御したパワー半導体のエネルギー損失の低減効果を実証するため、シリコンパワー半導体を駆動する測定系を開発し、パワー半導体をスイッチング動作させることでパワー半導体のエネルギー損失を測定しました(図3)。

パワー半導体の出力を600V、80Aの条件にて駆動させる環境で、通常用いられる汎用的な駆動ICでゲート駆動したパワー半導体のエネルギー損失が約17.5mJだったところ、本ICチップでゲート駆動したパワー半導体のエネルギー損失は約9mJとなり、約49%低減しました。

図3 開発した「自動波形変化ゲート駆動ICチップ」でシリコンのパワー半導体を駆動してエネルギー損失の低減を実証するための測定系 (提供:東京大学生産技術研究所)

3.今後の予定

NEDOと本研究グループは本事業において、さらなる高耐圧パワー半導体のエネルギー損失を低減する自動最適化手法※5やセンシング誤差※6を改善したセンサー回路の開発、それらを搭載したゲート駆動チップICの開発と実証を進めます。これにより、2050年カーボンニュートラルへの道筋を示し、パワーエレクトロニクス機器の省エネ化による温室効果ガスの排出量削減に貢献します。

【注釈】

- ※1 ノイズ

- ここでは、パワー半導体のスイッチング時に生じる、瞬間的に定常状態を超えて流れる大電流、または、発生する瞬時的な高電圧を指します。このような大電流や高電圧は、パワー半導体の破壊原因となります。

- ※2 パワー半導体を制御する手段

- Y. Wen, Y. Yang, and Y. Gao, “Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules,” IEEE Trans. on Power Electron., vol. 36, no. 2, pp. 1491-1505, Feb. 2021.

- ※3 省エネエレクトロニクスの製造基盤強化に向けた技術開発事業

-

- 事業名:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業/新世代パワー半導体の開発/大口径インテリジェント・シリコンパワー半導体の開発【委託事業】

- 事業期間:2021年度~2025年度

- 事業概要:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業

- ※4 600V、80Aの条件でエネルギー損失を約49%低減できることを確認

- 本研究成果は、2023年3月19日から23日まで米国・オーランドで開催されるIEEE Applied Power Electronics Conference and Exposition (APEC) 2023 で発表されました(論文タイトル:“Digital Gate Driver IC with Fully Integrated Automatic Timing Control Function in Stop-and-Go Gate Drive for IGBTs”)。

- ※5 自動最適化手法

- パワー半導体の状態に応じてエネルギー損失とノイズのバランスを自動で最適化する手法です。

- ※6 センシング誤差

- パワー半導体の状態を示す温度や電圧などの測定誤差を指します。

4.問い合わせ先

(本ニュースリリースの内容についての問い合わせ先)

NEDO IoT推進部 担当:野村(重)、功刀(くぬぎ)、須田 TEL:044-520-5211

(その他NEDO事業についての一般的な問い合わせ先)

NEDO 広報部 担当:根本、坂本、黒川、鈴木、橋本