2021/3/29 英国・ランカスター大学

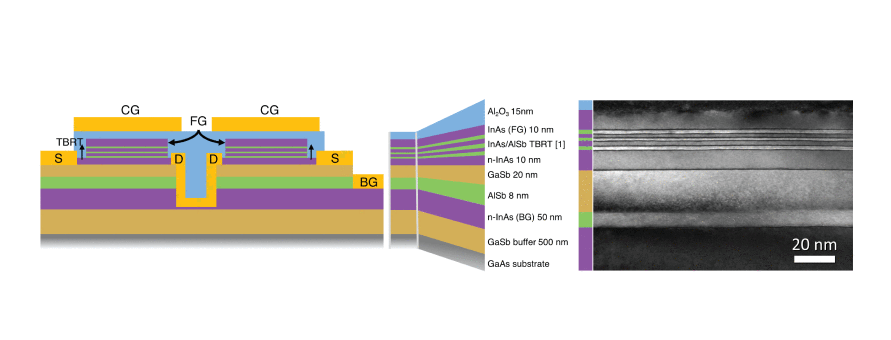

・ ランカスター大学が、独自に開発する新型のユニバーサルメモリの「ULTRARAMTM」を初めて小型(4-bit)アレイに集積し、次世代 ULTRARAMTM メモリチップのベースとなる新たなメモリアーキテクチャの実証に成功。

・ 共鳴トンネル効果を最大に活用できるようデバイス設計を変更し、初期プロトタイプの 2,000 倍の速度に加え、データ保持への影響無く、フラッシュメモリの最低でも 10 倍の P/E サイクルを達成した。

・ 今回の成果は、同メモリの驚異的な特性を確証し、高速、効率的で高エンデュランスの不揮発性メモリとしてのポテンシャルを示すもの。

・ メモリには、それぞれの特性と役割が相補的な関係にある、ダイナミック・ランダム・アクセス・メモリ(DRAM)とフラッシュメモリの 2 種類がある。

・ 高速の DRAM は能動メモリに使用されるが、揮発性のため電源が切れるとデータが失われる。一方、不揮発性のフラッシュメモリではデータの持ち運びを可能にするが、非常に遅く経時的に劣化する。データの保持には適するが、能動メモリとして使用できない。

・ 不揮発性 RAM である ULTRARAMTM(特許出願中)は、ユニバーサルメモリとして DRAM とフラッシュの両メモリの利点の特性を有するもの。

URL: https://www.lancaster.ac.uk/news/-first-steps-towards-revolutionary-ultraram-memory-chips

<NEDO海外技術情報より>

(関連情報)

IEEE Transactions on Electron Devices 掲載論文(フルテキスト)

ULTRARAM: Toward the Development of a III-V Semiconductor, Nonvolatile, Random Access

Memory

URL: https://ieeexplore.ieee.org/document/9387168