クラウドではなくユーザー側のAI処理で、プライバシーや安全、快適さを実現へ/AI新価値の共創を目指しオープンイノベーション環境を整備

2018-06-18 国立研究開発法人新エネルギー・産業技術総合開発機構,北海道大学,パナソニックセミコンダクターソリューションズ(株)

NEDOは、産業技術総合研究所、パナソニックセミコンダクターソリューションズ(株)、北海道大学とともに、アナログ抵抗変化素子を用いたAI半導体向けの脳型情報処理回路を開発し、世界最高水準の低消費電力動作の実証に成功しました。

今後、この回路の実用化により、身の回りのさまざまな電子機器に深層学習(推論/学習)を実装する場合、クラウド側に頼らずユーザー(エッジ)側だけで、負荷の大きな学習処理も実行できるようになります。個人情報をクラウドに上げることなくプライバシーに配慮したAI学習を進めることや、さらには、エネルギー分野や交通分野などの社会インフラの分散制御・高度化にも広く波及していくものと期待されます。

脳型情報処理回路を搭載したAI半導体は、その低消費電力性能から従来とは異なる利用機会やアプリケーションをもたらすことが見込まれます。NEDOと研究グループは、この新しい技術の普及促進やユーザーとの価値共創を目指し、AI開発環境である脳型情報処理活用プラットフォームの本格運用の開始や、関連技術の習得を目指した人材育成スクールの開催を2018年8月に予定しています。

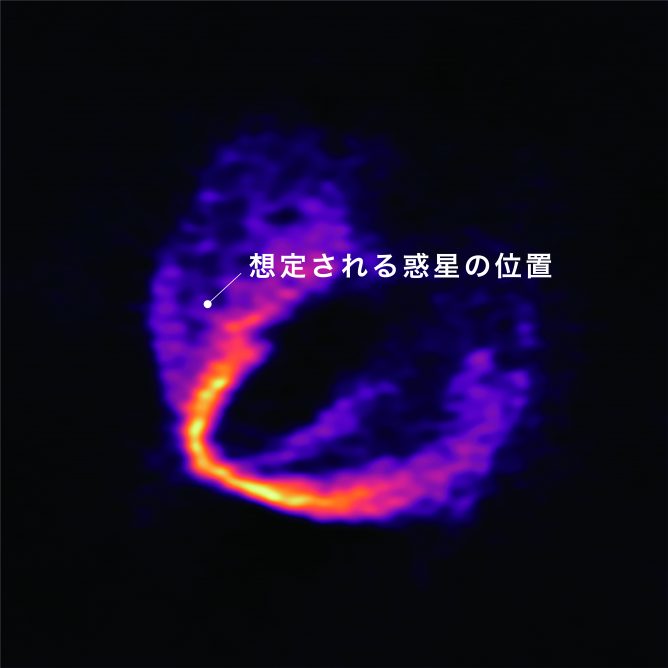

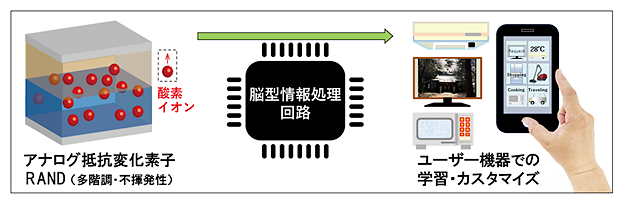

図1 本研究開発の成果のイメージ

1.概要

現在、AIを活用した家電やロボットが登場し、今後はさらに身の回りの電子機器へのAI実装が進むと予想されています。しかし、AIにおける学習の処理は演算量が膨大で消費電力が大きく、ユーザー機器(エッジ)側で処理することは容易ではありません。大量処理が可能なサーバー群で構成するクラウドシステム側でAIを搭載しエッジ側はクラウドの処理結果を受け取るだけ、もしくは、学習処理をクラウド側、推論(実行)処理をエッジ側で分担して行うというのが現状です。

今後、エッジ側で推論処理のみならず学習処理を実装することができるようになれば、個人情報をクラウドに上げることなくプライバシーに配慮したAI学習を進めたり、個人の端末でリアルタイム映像データ解析処理を可能としたり、さらには、エネルギー分野や交通分野などの社会インフラの分散制御・高度化にも広く波及して行くものと期待されます。そこで、NEDOは、AI半導体の基本回路構成自体に非連続的イノベーションを実現し、情報処理に要する消費電力を劇的に低減することを目的に、NEDO事業※1において、脳型※2AI処理システムの研究開発テーマを推進しています。

今般、NEDOと産業技術総合研究所、パナソニックセミコンダクターソリューションズ株式会社、北海道大学は、アナログ抵抗変化素子(Resistive Analog Neuro Device: RAND)※3を用いたAI半導体向けの脳型情報処理回路を開発し、世界最高水準の低消費電力動作の実証に成功しました。従来、クラウド学習用、クラウド学習・推論兼用、クラウド推論用、エッジ推論用と分類分けしていたAI半導体に、新たに「エッジ学習・推論兼用」のカテゴリを切り開くものと位置付けています。今後、この技術をチップ実装する際の制御性や信頼性の向上を図ることで、全く新しい基本回路構成を持つ脳型AI半導体の実用化を進めていきます。

なお、本研究開発成果の一部は、米国ホノルルで現地時間2018年6月18日(月)から22日(金)まで開催される「2018 Symposia on VLSI Technology and Circuits」で発表されます。

また、NEDOと研究グループは、この新しい技術の普及促進やユーザーとの価値共創を目指し、脳型情報処理を体験できるArduino※4ベースのキットなどAI開発環境プラットフォームの本格運用の開始や、アナログ抵抗変化素子の作成も含む関連技術の習得を目指した人材育成スクール※5の開催を2018年8月に予定しています。

2.今回の成果

【1】アナログ抵抗変化素子(RAND)を用いた低消費電力脳型情報処理AI回路の開発

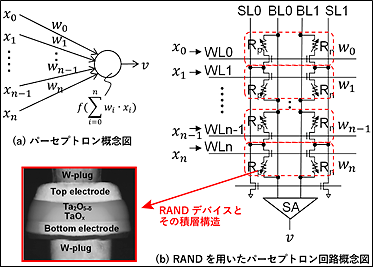

従来のAI半導体で用いられているデータ保存用メモリーと積和演算器が必要な方式に代わり、RANDによりデータ保存機能と積和演算機能を一体化したAI半導体向け脳型情報処理回路の開発に成功し、低消費電力動作を実証しました。RANDの積層構造(図2)は、すでに製品化されている不揮発性抵抗変化メモリー(Resistive Random Access Memory: ReRAM)※6を発展させ実用化を目指す構造にしており、パナソニックセミコンダクターソリューションズ(株)が保有するReRAM製造プロセスを応用して、開発しました。

脳型情報処理回路では多階調の学習データ保存※7が動作の鍵を握りますが、線幅180ナノメートルプロセスで開発したRAND(図3・左)では、30マイクロアンペアのダイナミックレンジで、ほぼ全てのデータ※8が、目標値の±2マイクロアンペアの範囲内に設定できるという良好な制御性を示しました。この結果、RANDによる脳型情報処理回路の文字認識率※9は90%を超え、実用化への道筋が確立されました。さらに線幅40ナノメートルプロセスで開発したRANDのテストチップ(図3・右)では、セル電流の低電流化に成功し、66.5 TOPS/W(Tera Operations per Second per Watt) ※10という世界最高水準の低消費電力動作を確認しました。これは、AI半導体の「エッジ学習・推論兼用」という新カテゴリを築くのに十分な値です。

図2 アナログ抵抗変化素子を用いたパーセプトロン回路

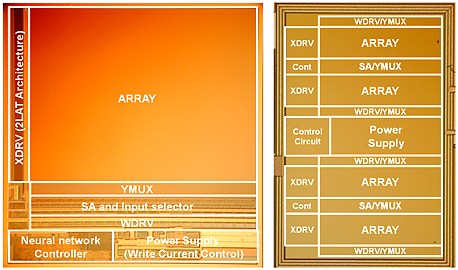

図3 アナログ抵抗変化素子を用いたAI半導体向けの脳型情報処理回路

[左]180nmプロセスの脳型情報処理回路

[右]40nmプロセスの消費電力評価テストチップ

【2】脳型情報処理回路を搭載したAI半導体のオープンイノベーション促進

脳型情報処理回路を搭載した低消費電力AI半導体は従来とは異なる利用機会やアプリケーションユーザー価値をもたらすことが期待されます。そこでNEDOと研究グループは、この新しい技術による身の回りのあらゆる電子機器へのAI搭載普及の促進やユーザーとの価値共創を目指して、脳型情報処理回路を用いたAIを広く利活用できる環境の整備を進めています。その一環として、個人・小規模チーム開発者や一般ユーザー、学生等、誰でも容易にAIを体験・実験できる脳型情報処理活用プラットフォーム※11の本格運用の開始や、アナログ抵抗変化素子の作成も含む関連技術の習得を目指した人材育成スクールの開催を予定しています。

プラットフォームの利用にあたり適時開催する体験セミナーの参加者は、半日弱という短い時間で、機動力の高いソフト・ハード一体オープンイノベーションの仕組みと、そこで動作するさまざまなサンプルAIプログラムを実際に体験することができます。

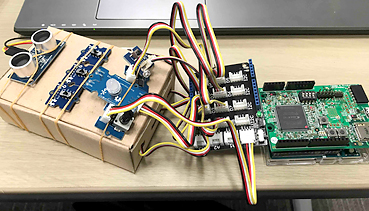

具体的には、SDカードによりAIアプリケーションの変更が可能な、AIに特化したメモリーアーキテクチャを持つ「FPGA(Field-Programmable Gate Array)※12 AIシールド※13」と、Arduinoマイコンを標準的なSPI(Serial Peripheral Interface)※14で接続した「ソフト・ハード協調システム」(図4)を用いて、ハードウェアAIが実現する無限の可能性を容易かつ身近に体験できるようになっています。

また、FPGA AIコアのHDL(Hardware Description Language)※15およびArduinoの制御コードからなるサンプルライブラリ一式をオープンソースとして利用者が活用でき、さらにはその成果物を情報発信できるようなクラウドシステムも構築しています。

図4 ソフト・ハード協調システムの一例

3.今後の予定

今回の研究成果により、RANDの微細化が、AI半導体向け脳型情報処理回路の低消費電力化を進める上で大きな効果を持つことが確認されました。今後は、小型で低消費電力であることが強みとなるエッジ処理に用いることを想定した脳型AI半導体の実用化研究を推進し、さらなる微細化の追求、制御性や信頼性の向上を目指した研究開発も進めていきます。

また、RANDの制御性が高いことも明らかになったことから、適用アプリケーション領域の拡大を目指して、さまざまな深層学習手法に対応できるFNA(Flexible Network Architecture)※16としての開発も進めます。

2018年8月に予定している、脳型情報処理活用プラットフォームの本格運用開始や関連技術の習得を目指した人材育成スクールの開催の詳細については、6月下旬頃に本研究開発テーマのポータルサイトで公表予定です。

- NEDO IoT推進のための横断技術開発プロジェクト

【注釈】

- ※1 NEDO事業

- 事業名:高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発(AIC事業)

(2017年度までの事業名:IoT推進のための横断技術開発プロジェクト)

テーマ名:超高速・低消費電力ビッグデータ処理を実現・利活用する脳型推論集積システムの研究開発

事業期間:2016年度~2020年度 - ※2 脳型

- 従来のノイマン型コンピューティングに対し、認識問題を解くことに優れ低消費電力で動作する脳の機能を再現することを目指したコンピューティング形式。

- ※3 アナログ抵抗変化素子(Resistive Analog Neuro Device: RAND)

- 不揮発性抵抗変化メモリー(Resistive Random Access Memory: ReRAM※6)と同じ金属/酸化物/金属積層構造からなり、電圧パルスを印加する等により、酸化物層を挟んだ金属電極間の抵抗が連続的に変わり、神経を模した機能を備えた電子デバイス。

- ※4 Arduino

- 広く用いられているマイコンボードの1つ。製品情報等は下記のサイトから調べることができる。

- ※5 人材育成スクール

- 脳型情報処理活用プラットフォームで開催しているスクール。材料、デバイス、プロセス、アーキテクチャ開発という「縦糸」と、データの収集(センサーネット、高速通信等)、蓄積(サーバーからクラウドまで)、処理(脳型推論、量子情報処理、特に、ソフトとハードの一体的開発の視点からアーキテクチャを含む)、そしてデータセキュリティに関する基礎から応用までの横断的テーマを「横糸」にしたカリキュラムとなっており、AIC事業に参画する複数の事業者が協力して開催している。

- NEDO IoT推進のための横断技術開発プロジェクト

なお、2018年度から、日本工学会CPD協議会のECEプログラムとしての認定を受けて開催する。

略語説明 CPD: Continuing Professional Development

略語説明 ECE: Engineering Capacity Enhancement - ※6 不揮発性抵抗変化メモリー(Resistive Random Access Memory: ReRAM)

- 金属/酸化物/金属積層構造からなり、酸化物層を挟んだ金属電極間に、電圧(電流)を印加することにより生じる不揮発な抵抗変化を利用したランダムアクセスメモリー。Resistance Random Access Memory、あるいはResistive Random Access Memoryの頭文字をとってReRAM(アールイーラム、あるいはリラム)と呼ばれている。 産業技術総合研究所では、ReRAMの動作メカニズム解明と低消費電力化に向けた研究開発が進められてきた。(参考:産業技術総合研究所 研究成果記事「抵抗変化メモリーの挙動を電流ノイズから解明」2017年1月13日)

パナソニックセミコンダクターソリューションズ(株)では、世界に先駆けてReRAMの製品化に成功し、ReRAMが搭載された超低消費電力マイコンを商品化している。

- ReRAM搭載 超低消費電力マイコン MN101L(パナソニック)

- ※7 多階調の学習データ保存

- 脳型情報処理回路では、ニューラルネットワーク(深層学習で用いる脳の認知機能を模した情報処理モデル)で学習の結果で決定するニューラルネットワークの変数である重み値を情報処理回路の抵抗値として保存する。このため、再現性よく保存できる重み値の階調数が深層学習の推論性能に影響する。

- ※8 ほぼ全てのデータ

- 標準偏差で表現すると、「1シグマで定義される揺らぎが0.59マイクロアンペア」。

- ※9 文字認識率

- ここでは、深層学習の性能評価でよく用いられるMNISTデータセット(手書きで書かれた数字の画像と正解数字のデータセット)を使用して画像認識させた時の正答率。

- ※10 TOPS/W (Tera Operations per Second per Watt)

- 単位ワット、1秒あたりの演算性能。

- ※11 脳型情報処理活用プラットフォーム

- 低電力で小型の脳型情報処理ハードウェアを様々なユーザーが活用できる環境、デバイスの試作環境、安価・柔軟・高速な共通ハードウェアボードとその開発環境、クラウドベースの情報共有システム等からなるプラットフォーム。試行(ベータ)版を2018年3月23日より運用開始した。また、実習を含むスクール等も開催し、ユーザードリブン型の価値創造を目指している。

- ※12 FPGA(Field-Programmable Gate Array)

- 購入者や設計者が、集積回路の機能を何度も繰り返して再構成できる半導体チップ。FPGAでは、製造後であっても、外部から設計情報を書き込むことによって、任意の論理回路を構成することができる。

- ※13 シールド

- Arduino用の機能拡張基板のこと。

- ※14 SPI(Serial Peripheral Interface)

- コンピュータ内部で使われるデバイス同士を接続するバスのこと。

- ※15 HDL(Hardware Description Language)-

- ハードウェア記述言語。半導体チップの回路設計等を行なうために用いる。

- ※16 FNA(Flexible Network Architecture)

- さまざまな種類のニューラルネットワーク(深層学習で用いる脳の認知機能を模した情報処理モデル)を動作させることのできるAI回路構成のこと。

4.問い合わせ先

(本ニュースリリースの内容についての問い合わせ先)

NEDO IoT推進部 担当:大西、山本

(その他NEDO事業についての一般的な問い合わせ先)

NEDO 広報部 担当:藤本、坂本、髙津佐