2025-06-25 東京科学大学

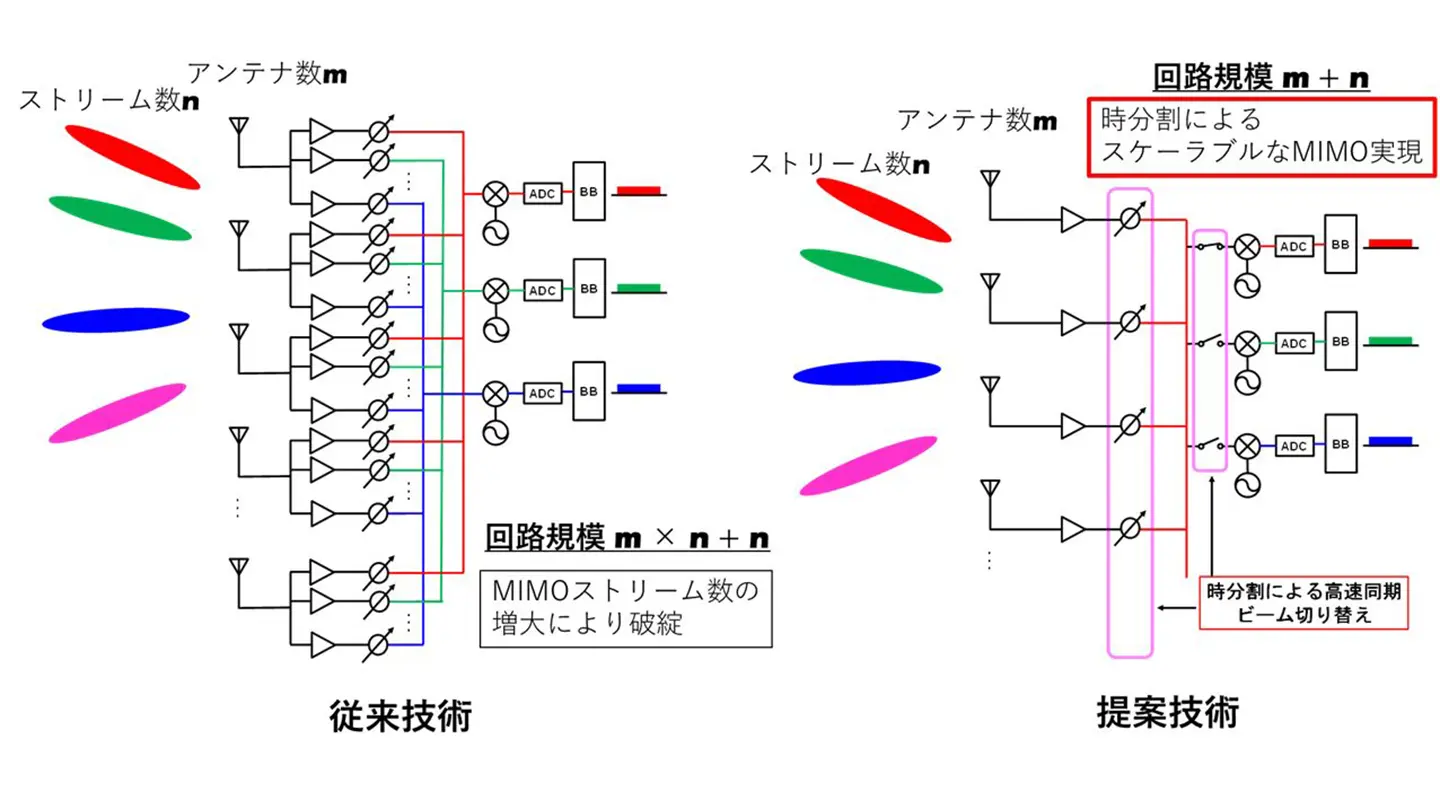

図1. 開発した時分割MIMOフェーズドアレイ技術と従来技術の比較

図1. 開発した時分割MIMOフェーズドアレイ技術と従来技術の比較

<関連情報>

6Gアプリケーションのためのタイムホッピングブロッカー除去Kaバンド8ストリームフェーズドアレイ受信機 A Ka-Band 8-Stream Phased-Array Receiver with Time-Hopping Blocker Rejection for 6G Applications

M. Tang, Y. Zhang, D. Xu, Y. Liu, Z. Li, Y. Chen, M. Fan, Z. Ren, J. Pang, D. Xu, C. Liu, Y. Zhang, H. Sakai, K. Kunihiro, A. Shirane and K. Okada

2025 Symposium on VLSI Technology and Circuits 開催期間:6月8日~12日

説明

この研究では、わずか8個のRF素子を使用して最大8つのストリームをサポートする、面積効率の高いKaバンド非均一時間ホッピング(TH)フェーズドアレイ受信機を提案する。高速ストリーム切り替えにより異なるストリームのRF信号パスを再利用することにより、この設計ではチップ面積を大幅に削減する。さらに、提案された非均一TH技術は、ディザリングによるスイッチング高調波によって引き起こされるブロッカ問題を軽減する。65nm CMOSで製造されたプロトタイプは、水平偏波と垂直偏波の両方でOTA測定による4×4 MIMO信号受信を実証し、ブロッカ耐性が42.9 dB向上して合計データレート38.4 Gbpsを達成した。

This work proposes an area-efficient Ka-band non-uniform time-hopping (TH) phased array receiver that supports up to eight

streams using only eight RF elements. By reusing RF signal paths for different streams through fast stream switching, the

design significantly reduces chip area. Additionally, the proposed non-uniform TH technique mitigates blocker issues caused

by switching harmonics through dithering. A prototype fabricated in 65nm CMOS demonstrates 4×4 MIMO signal reception in

OTA measurements for both horizontal and vertical polarization, achieving a total data rate of 38.4 Gbps with a 42.9 dB

improvement in blocker tolerance