2025-05-29 東京科学大学

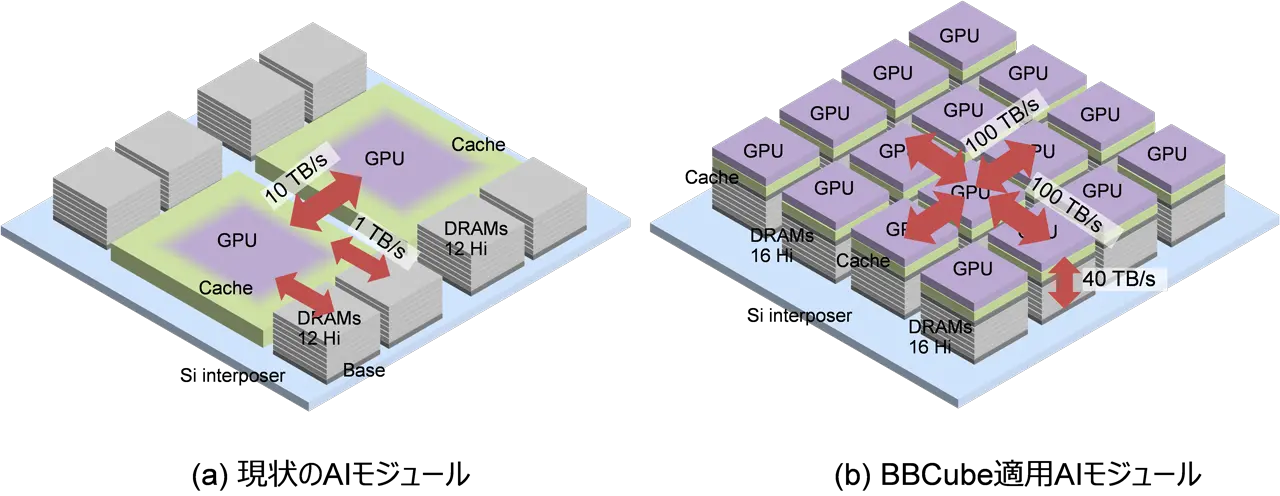

東京科学大学(Science Tokyo)は、次世代3次元半導体実装技術「BBCube™」の実用化に向け、三つの革新技術を開発しました。第一に、直径300mmのワッフルウェーハ上に3万個以上のチップを10ms以下で実装可能な高速・高精度なChip-on-Wafer(COW)プロセスを確立。第二に、表面処理剤を不要とし、片面塗布・室温圧着が可能な新規接着剤「DPAS300」を開発。第三に、高密度コンデンサ層を演算チップと積層メモリの間に挟み込む新たな電源供給アーキテクチャを構築し、電源ノイズを50mV以下に抑制することに成功しました。これらの成果は、スマートフォンやスーパーコンピュータなどの電子機器の高性能化と省電力化に貢献することが期待されます。

<関連情報>

バンプレスCOW(Chip-an-Wafer)パッケージのためのワッフルウェハ上のフェースダウンおよび異種チップ接合技術 Face-Down and Heterogeneous Chip Bonding Technology on Waffle-Wafer for Bumpless Chip-an-Wafer (COW) Package

Yoshiaki Satake; Tatsuya Funaki; Wataru Doi; Hajime Kato; Shogo Okita; Takayuki Ohba

2024 International 3D Systems Integration Conference (3DIC) Date of Conference: 25-27 September 2024

DOI:https://doi.org/10.1109/3DIC63395.2024.10830233

Abstract:

A high-speed, manufacturable, fully chiplet integration process using Face-Down bonding to 300 mm waffle-wafer and bumpless Chip-on-Wafer (COW) has been developed for the first time. The inkjet method successfully formed a thin adhesive layer on the bottom of the waffle wafer, with no voids even at a 5 μm adhesive thickness. Over 30,000 chips with a narrow gap of 40 μ m were bonded with a misalignment of less than 10 μ m and a short bonding time of a few milliseconds per chip.