2025-03-28 シンガポール国立大学(NUS)

<関連情報>

- https://news.nus.edu.sg/advancing-semiconductor-devices-for-artificial-intelligence/

- https://www.nature.com/articles/s41586-025-08742-4

標準的なシリコン・トランジスタにおけるシナプスと神経行動 Synaptic and neural behaviours in a standard silicon transistor

Sebastian Pazos,Kaichen Zhu,Marco A. Villena,Osamah Alharbi,Wenwen Zheng,Yaqing Shen,Yue Yuan,Yue Ping & Mario Lanza

Nature Published:26 March 2025

DOI:https://doi.org/10.1038/s41586-025-08742-4

Abstract

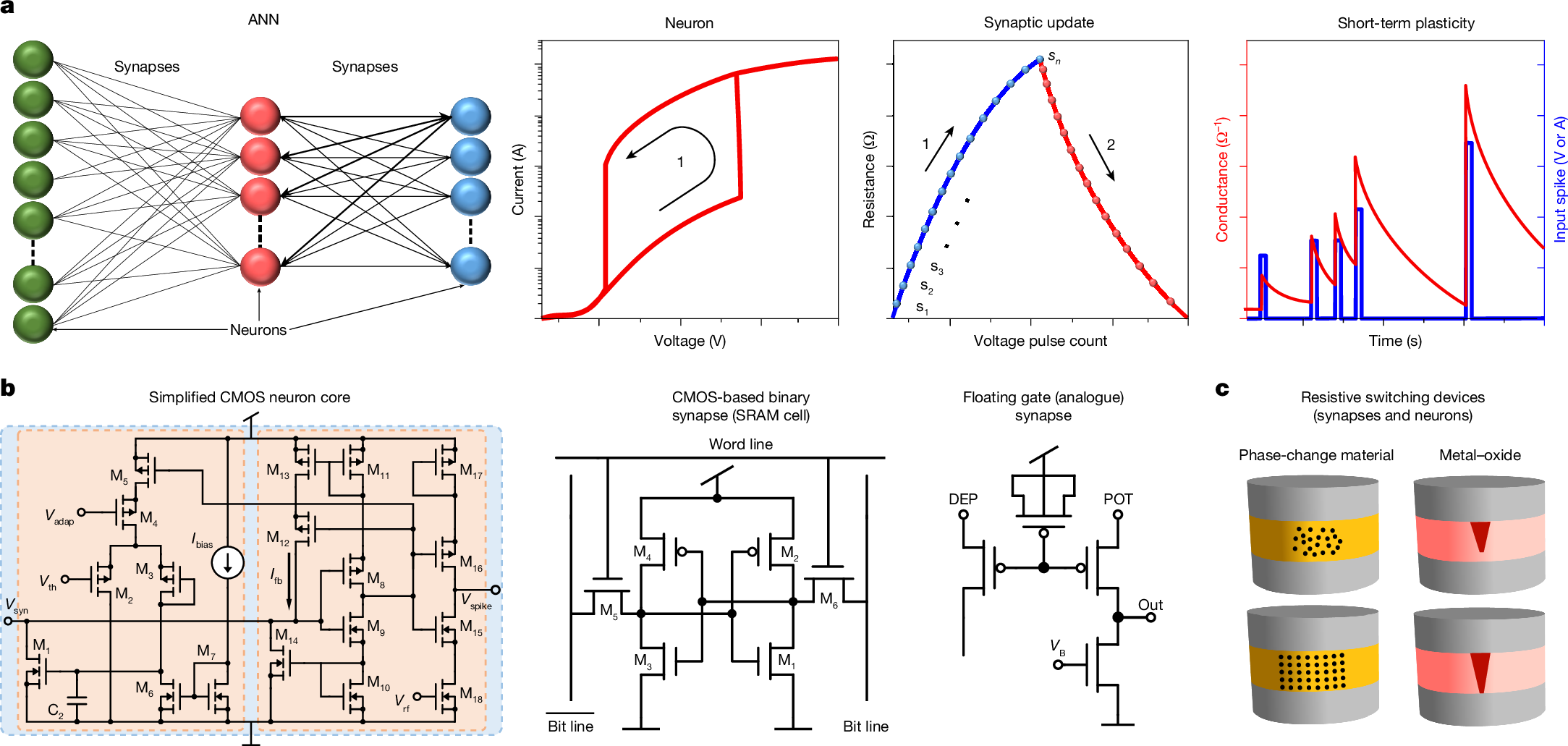

Hardware implementations of artificial neural networks (ANNs)—the most advanced of which are made of millions of electronic neurons interconnected by hundreds of millions of electronic synapses—have achieved higher energy efficiency than classical computers in some small-scale data-intensive computing tasks1. State-of-the-art neuromorphic computers, such as Intel’s Loihi2 or IBM’s NorthPole3, implement ANNs using bio-inspired neuron- and synapse-mimicking circuits made of complementary metal–oxide–semiconductor (CMOS) transistors, at least 18 per neuron and six per synapse. Simplifying the structure and size of these two building blocks would enable the construction of more sophisticated, larger and more energy-efficient ANNs. Here we show that a single CMOS transistor can exhibit neural and synaptic behaviours if biased in a specific (unconventional) manner. By connecting one additional CMOS transistor in series, we build a versatile 2-transistor-cell that exhibits adjustable neuro-synaptic response (which we named neuro-synaptic random access memory cell, or NS-RAM cell). This electronic performance comes with a yield of 100% and an ultra-low device-to-device variability, owing to the maturity of the silicon CMOS platform used—no materials or devices alien to the CMOS process are required. These results represent a short-term solution for the implementation of efficient ANNs and an opportunity in terms of CMOS circuit design and optimization for artificial intelligence applications.