CMOS半導体プロセス親和性と量子ドット安定動作を両立

2020-04-27 株式会社日立製作所

日立は、量子コンピュータの大規模集積化につながるシリコン半導体を用いた量子ビット*1アレイの基本構造の試作に成功しました。従来、量子コンピュータは、大規模集積化に伴い、量子ビットを動作させるための信号配線数が増えることで小型化が困難でした。本アレイでは、CMOS半導体回路技術*2を応用し、複数の量子ビットを制御する信号配線を共通化することで、配線数の増加を抑制しながら量子ビットを2次元状に配列して大規模集積化を実現することを試みました。今回、量子計算の際に電子を閉じ込める箱となる量子ドット*3をアレイ上の所望の位置に安定的に形成できることを確認しました。今後、日立は、本アレイ構造を用いて量子計算の実証に取り組み、大規模集積化が可能なシリコン量子コンピューターの開発を加速させていきます。

背景および取り組んだ課題

- 量子コンピュータでは、複雑な計算を解くために量子ビットを大規模に集積することが重要であり、この大規模集積化の実現により、高速および高効率での新材料や製薬の設計・開発や、金融リスク計算や投資評価など、さまざまな分野への適用が期待できる。

- これまで日立では、CMOS半導体回路技術を用いたシリコン量子コンピュータの実現に向けて、日立ケンブリッジ研究所を中心に研究開発を進めてきた*4。

開発した技術

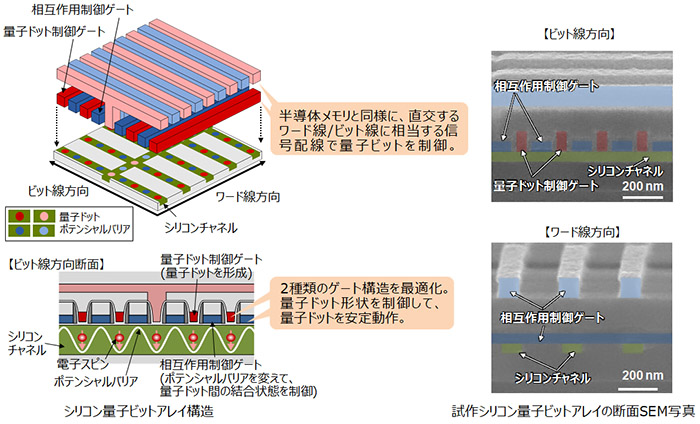

- 小型で大規模集積化を可能にする2次元量子ビットアレイ構造

- 半導体回路を用いた安定動作を実現する量子ビット構造

確認した効果

- 本アレイ構造を試作して動作検証したところ、共通化したゲート電極を用いて、アレイ内の所望の位置に量子ドットを形成できることを確認。

- 量子ドット形状を制御することで、多数の量子ビットを半導体回路で動作させるための十分な電圧ージン(0.2V*5)を確保しながら、量子計算を行う上で必要な2重量子ドット結合状態*6を安定的に得られることを確認。

2次元シリコン量子ビットアレイ構造(左図)と試作した量子ビットアレイの断面写真(右図)

発表する論文、学会、イベントなど

本成果は、科学誌「Applied Physics Letters」(2020年4月23日付:日本時間4月24日)にFeatured Articleとして掲載済。

謝辞

本成果の一部は東京工業大学との共同研究の結果得られたものです。

開発した技術の詳細

1. 小型で大規模集積化を可能にする2次元量子ビットアレイ構造

量子ビット数の増加に伴い、それぞれのビットを動作させるための信号配線数が増え、小型化できないことが大規模集積化に向けた課題となっていました。本アレイでは、SRAMやDRAM*7などの半導体メモリと同様に直交するワード線/ビット線*8に相当する信号配線で、複数の量子ビットを形成する素子、および、量子ビット間の結合を制御する構造にしました。このように信号配線を共通化することで、配線数の増加を抑制しながら量子ビットの大規模集積化が可能となります。

2. 半導体回路を用いた安定動作を実現する量子ビット構造

半導体回路を用いて多数の量子ビットを安定に動作させるために、量子計算に必要となる量子ドットを形成し、制御する際の電圧マージンを確保することが課題となっていました。今回、上記した2種類のゲート電極のゲート長や位置関係などの構造と、それぞれのゲート電極に加える電圧を最適化することで、量子ドットの安定動作が可能となりました。

- *1

- 量子ビット: 量子情報の最小単位のこと。従来のデジタル回路では“0”もしくは“1”の2状態に情報が保持される(古典ビット)。一方、量子ビットでは“0”でありかつ“1”でもある状態を、任意の割合で組み合わせて表現できる。

- *2

- CMOS半導体回路技術: LSI、メモリーなどの大規模集積回路に使用されるディジタル回路方式

- *3

- 量子ドット: 電子を空間的に3次元全ての方向に閉じ込め移動方向が制限された電子の状態のこと

- *4

- Research team led by the Hitachi Cambridge Laboratory demonstrates an innovative hybrid circuit for quantum computers (2019年6月18日), https://www.hitachi.com/New/cnews/month/2019/06/190618a.html

- *5

- 従来比10倍の電圧マージン、日立調べ(2020年3月時点)

- *6

- 2重量子ドット結合: 2つの量子ドットをが互いに連結した量子ドット状態。量子計算を実行する上で2量子ビットを用いた論理ゲート操作が必要となる。

- *7

- SRAM/DRAM: 半導体メモリの一種。SRAMは、定期的なリフレッシュ(回復動作)が不要なのに対して、DRAMは、リフレッシュをこの行うことで情報を保持する。

- *8

- ワード線/ビット線: 2次元状に並んだメモリーセルアレイの中から一列を選択するための制御信号線。メモリーセルは、ワード線とビット線の交点に置かれており、読み出し/書き込みを行なうアドレスに対応するワード/ビット線を制御することで、書き込み/読み出しが可能になる。SRAM/DRAM等で用いられる。

照会先

株式会社日立製作所 研究開発グループ