2023-11-14 スイス連邦工科大学ローザンヌ校(EPFL)

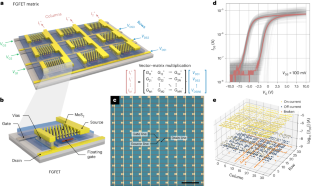

◆このプロセッサは2D MoS2トランジスタと浮動ゲートを組み合わせ、ベクトルマトリックスの乗算などの基本的なデータ処理操作に対応しています。この成果は、スイスとEUの密接な協力の結果であり、半導体技術における欧州の競争力を強化するための取り組みに貢献しています。

<関連情報>

- https://actu.epfl.ch/news/redefining-energy-efficiency-in-data-processing/

- https://www.nature.com/articles/s41928-023-01064-1

単層二硫化モリブデンメモリをベースにした A large-scale integrated vector–matrix multiplication processor based on monolayer molybdenum disulfide memories

Guilherme Migliato Marega,Hyun Goo Ji,Zhenyu Wang,Gabriele Pasquale,Mukesh Tripathi,Aleksandra Radenovic & Andras Kis

Nature Electronics Published:13 November 2023

DOI:https://doi.org/10.1038/s41928-023-01064-1

Abstract

Data-driven algorithms—such as signal processing and artificial neural networks—are required to process and extract meaningful information from the massive amounts of data currently being produced in the world. This processing is, however, limited by the traditional von Neumann architecture with its physical separation of processing and memory, which motivates the development of in-memory computing. Here we report an integrated 32 × 32 vector–matrix multiplier with 1,024 floating-gate field-effect transistors that use monolayer molybdenum disulfide as the channel material. In our wafer-scale fabrication process, we achieve a high yield and low device-to-device variability, which are prerequisites for practical applications. A statistical analysis highlights the potential for multilevel and analogue storage with a single programming pulse, allowing our accelerator to be programmed using an efficient open-loop programming scheme. We also demonstrate reliable, discrete signal processing in a parallel manner.