2023-02-18 東京工業大学,科学技術振興機構

ポイント

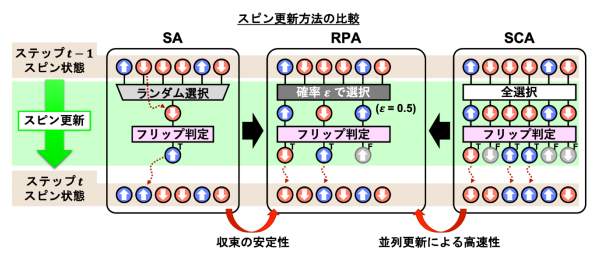

- 組み合わせ最適化問題の性質と最適なアニーリング計算原理の相関を調査

- 複数の計算原理を選択的に利用できる計算機構造を設計

- アニーリングプロセッサLSIを試作し、計算の高速化と省エネ化を実証

東京工業大学 科学技術創成研究院の本村 真人 教授、川村 一志 特任助教らは、北海道大学、京都大学と共同で、スマート社会の発展に不可欠な組み合わせ最適化問題を高効率に解決するアニーリングプロセッサLSIを新規に開発した。

国内外でのアニーリングマシン研究開発競争が激化する昨今、求解対象の組み合わせ最適化問題をどの計算原理・マシンで解くのがベストであるのかを明確にし、アニーリングマシンの早期実用化を進めることが求められている。本研究では、問題の性質と最適な計算原理の相関を調査するとともに、複数の計算原理を選択的に利用可能な計算機構造、並びに、それを具現化したプロセッサLSI「Amorphica」を開発した。求解対象の問題に合わせて計算原理を選択できるようにすることで、多様な問題に対して最適な計算原理を適用することが可能になる。さらに、本LSIを複数個接続することで大規模な問題を求解可能である。AmorphicaをGPU(画像処理半導体)と比較したところ、最大58倍の高速化を達成するとともに、およそ3万倍の電力効率を達成した。

本研究成果の詳細は、2023年2月19日~23日(現地時間)に米国サンフランシスコで開催される「ISSCC 2023(国際固体素子回路会議)」にて発表される(発表者:川村 一志)。ISSCCは集積回路に関する最難関国際会議で、世界中から最高峰の研究成果が発表される。

本研究開発は、以下の助成事業により推進されたものである。

科学技術振興機構(JST) 戦略的創造研究推進事業 CREST「Society5.0を支える革新的コンピューティング技術」

研究総括

坂井 修一(東京大学 教授)

研究課題名

「学習/数理モデルに基づく時空間展開型アーキテクチャの創出と応用」

(JPMJCR18K3)

研究代表者

本村 真人(東京工業大学 科学技術創成研究院 教授)

<講演タイトル>

- “Amorphica: 4-Replica 512 Fully Connected Spin 336MHz Metamorphic Annealer with Programmable Optimization Strategy and Compressed-Spin-Transfer Multi-Chip Extension”

<お問い合わせ先>

<研究に関すること>

本村 真人(モトムラ マサト)

東京工業大学 科学技術創成研究院 AIコンピューティング研究ユニット 教授

<JST事業に関すること>

前田さち子(マエダ サチコ)

科学技術振興機構 戦略研究推進部 ICTグループ

<報道担当>

東京工業大学 総務部 広報課

科学技術振興機構 広報課