2026-02-14 東京大学

東京大学大学院工学系研究科の飯塚哲也教授らは、補正不要で低ジッタ・低スプリアスを同時に実現する新方式の分数分周PLLを開発した。二段カスケード構造において、二つのマルチモジュラス分周器による量子化雑音キャンセルと、初段発振器雑音を抑えるフィードフォワード型雑音キャンセルを組み合わせることで、従来必要だったDTC補正や複雑なデジタル処理を不要化。65nm CMOS試作チップで157fsのジッタ、–73dBcのスプリアス性能を実証し、出力周波数や分周比に依らない安定した低雑音特性を達成した。Beyond 5Gや6G向けの高性能周波数シンセサイザとしての応用が期待される。

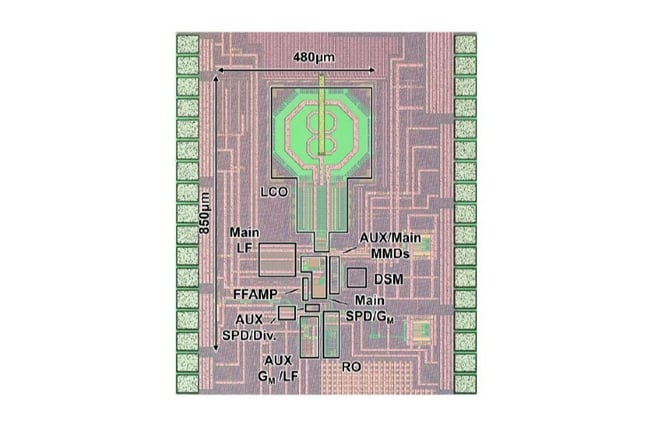

開発した新方式位相同期回路の65nmプロセスでの試作品写真

<関連情報>

157μsrmsジッタ、−73dBc微分スプリアス、校正不要のカスケードSPLL堅牢なフィードフォワードノイズキャンセルとMMDベースの量子化誤差キャンセルを採用60MHz基準電圧駆動 A 157fsrms-Jitter, −73dBc-Fractional-Spur, Calibration-Free Cascaded SPLL Employing Robust Feedforward Noise Cancellation and MMD-Based Quantization-Error Cancellation with a 60MHz Reference

Haoming Zhang, Yongjuan He, Yuyang Zhu, Huanyu Ren, and Tetsuya Iizuka

2026 IEEE International Solid-State Circuits Conference Date Added to IEEE Xplore:03 March 2026

DOI:https://doi.org/10.1109/ISSCC49663.2026.11409292

Abstract:

This work presents a 6.2-to-6.8GHz calibration-free fractional-N sampling PLL with cascaded architecture, achieving 157fsrms jitter and a −73dBc fractional spur using feedforward noise cancellation (FFNC) and MMD-based quantization-error cancellation (QEC). The QEC reduces Q-error by N, enabling a low-noise SPD for fractional-N operation. With both stages as SPLLs, the FFNC-path gain and the original-path gain inherently match regardless of division-ratio changes, ensuring robust cancellation of the first-stage VCO noise.