2025-10-31 東京科学大学

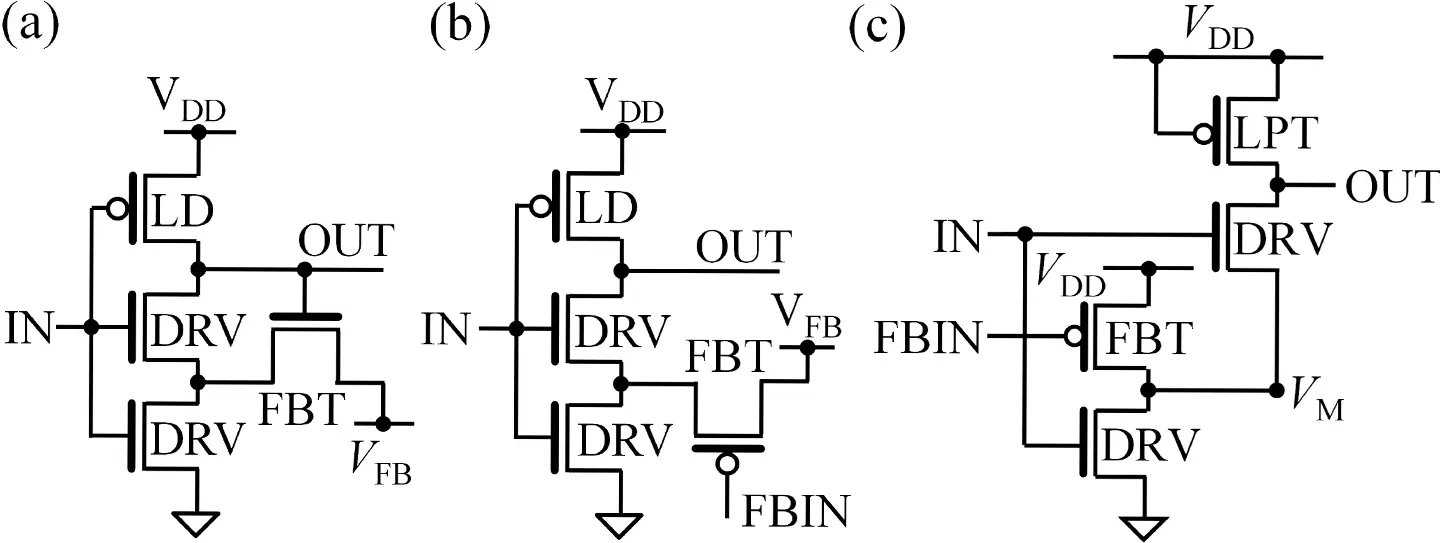

図1. (a)ST0、(b)ST1、(c) nST1インバータの回路構成

<関連情報>

- https://www.isct.ac.jp/ja/news/fjmc1c5crvok

- https://www.isct.ac.jp/plugins/cms/component_download_file.php?type=2&pageId=&contentsId=1&contentsDataId=2576&prevId=&key=176c2699c53412edc1e7616242ada268.pdf

- https://ieeexplore.ieee.org/document/11106369

ノイズ耐性を強化する新型超低電圧リテンションSRAMセル A New Ultralow-Voltage Retention SRAM Cell Enhancing Noise Immunity

Katsutoshi Ito; Yusaku Shiotsu; Satoshi Sugahara

IEEE Open Journal of Circuits and Systems Published:31 July 2025

DOI:https://doi.org/10.1109/OJCAS.2025.3594022

Abstract:

A new ultralow-voltage retention (ULVR) SRAM cell is proposed, which can highly enhance the noise margin (NM) for the ULVR mode at ultralow voltages (VUL) . This 8T cell is configured with new-type Schmitt-trigger (ST) inverters that can nearly maximize the hysteresis width of the voltage transfer characteristics (VTC). The design methodology of the cell is developed with careful consideration for the process variation of the constituent transistors, and the optimally designed cell can ensure sufficient NMs that satisfy the 6σ failure probability for all the operating modes. In particular, for the ULVR mode at VUL=0.2 V, the proposed 8T cell can exhibit much stronger noise immunity than previously proposed various low-voltage cells. In addition, the proposed 8T cell can achieve stable data retention even at VUL=0.16 V with sufficient noise immunity satisfying the 6σ failure probability. An 8kB ULVR-SRAM macro configured with the proposed-8T-cell array is also developed. Using the ULVR mode, the macro can reduce the standby power by ~93% compared with the standby mode of a conventional 6T-SRAM macro.